# Table of Contents-

| 1.       | GENE | ERAL D | DESCRIPTION                                                                      | 4  |

|----------|------|--------|----------------------------------------------------------------------------------|----|

| 2.       | FEAT | URES   |                                                                                  | 4  |

| 3.       | ORDE | ER INF | ORMATION                                                                         | 4  |

| 4.       | BALL | CONF   | GURATION                                                                         | 5  |

|          | 4.1  | E      | Ball Assignment: LPSDR x16                                                       | 5  |

|          | 4.2  |        | Ball Assignment: LPSDR x32                                                       |    |

| 5.       |      |        | RIPTION                                                                          |    |

| 0.       | 5.1  |        | Signal Description                                                               |    |

|          | 5.2  |        | Addressing Table                                                                 |    |

| 6.       | -    |        | GRAM                                                                             |    |

| 0.<br>7. |      |        | AL DESCRIPTION                                                                   |    |

| 1.       | 7.1  |        | Command Function                                                                 |    |

|          |      | 7.1.1  | Table 1. Truth Table (Note (1) and (2))                                          |    |

|          | -    | 7.1.2  | Functional Truth Table (See Note 1)                                              |    |

|          | -    | 7.1.3  | Functional Truth Table for CKE                                                   |    |

|          |      | 7.1.4  | Bank Activate Command                                                            |    |

|          | -    | 7.1.5  | Bank Precharge Command                                                           |    |

|          | -    | 7.1.6  | Precharge All Command                                                            |    |

|          |      | 7.1.7  | Write Command                                                                    |    |

|          | 7    | 7.1.8  | Write with Auto Precharge Command                                                |    |

|          | 7    | 7.1.9  | Read Command                                                                     |    |

|          | 7    | 7.1.10 | Read with Auto Precharge Command                                                 |    |

|          | 7    | 7.1.11 | Extended Mode Register Set Command                                               | 16 |

|          | 7    | 7.1.12 | Mode Register Set Command                                                        | 16 |

|          | 7    | 7.1.13 | No-Operation Command                                                             | 16 |

|          | 7    | 7.1.14 | Burst Stop Command                                                               | 16 |

|          | 7    | 7.1.15 | Device Deselect Command                                                          | 16 |

|          | 7    | 7.1.16 | Auto Refresh Command                                                             | 16 |

|          | 7    | 7.1.17 | Self Refresh Entry Command                                                       |    |

|          | 7    | 7.1.18 | Self Refresh Exit Command                                                        |    |

|          | -    | 7.1.19 | Clock Suspend Mode Entry/Power Down Mode Entry Command                           |    |

|          | -    | 7.1.20 | Clock Suspend Mode Exit/Power Down Mode Exit Command                             |    |

|          | -    | 7.1.21 | Data Write/Output Enable, Data Mask/Output Disable Command                       |    |

| 8.       | OPER |        | N                                                                                |    |

|          | 8.1  |        | Read Operation                                                                   |    |

|          | 8.2  |        | Vrite Operation                                                                  |    |

|          | 8.3  |        | Precharge                                                                        |    |

|          |      | 3.3.1  | Auto Precharge                                                                   |    |

|          |      | 3.3.2  | READ with auto precharge interrupted by a READ (with or without auto precharge)  |    |

|          | 8    | 3.3.3  | READ with auto precharge interrupted by a WRITE (with or without auto precharge) | 19 |

|     | 1    |       | winbond                                                                         |      |

|-----|------|-------|---------------------------------------------------------------------------------|------|

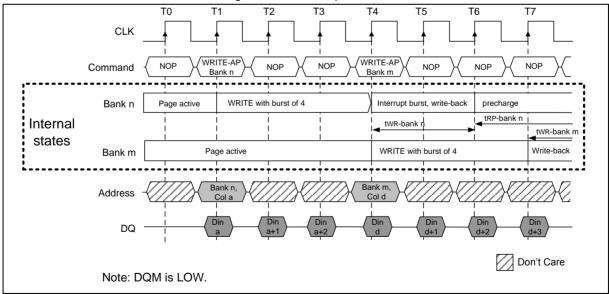

|     |      | 8.3.4 | WRITE with auto precharge interrupted by a READ (with or without auto precharge | )20  |

|     |      | 8.3.5 | WRITE with auto precharge interrupted by a WRITE (with or without auto precharg | e)20 |

|     | 8.4  |       | Burst Termination                                                               | 21   |

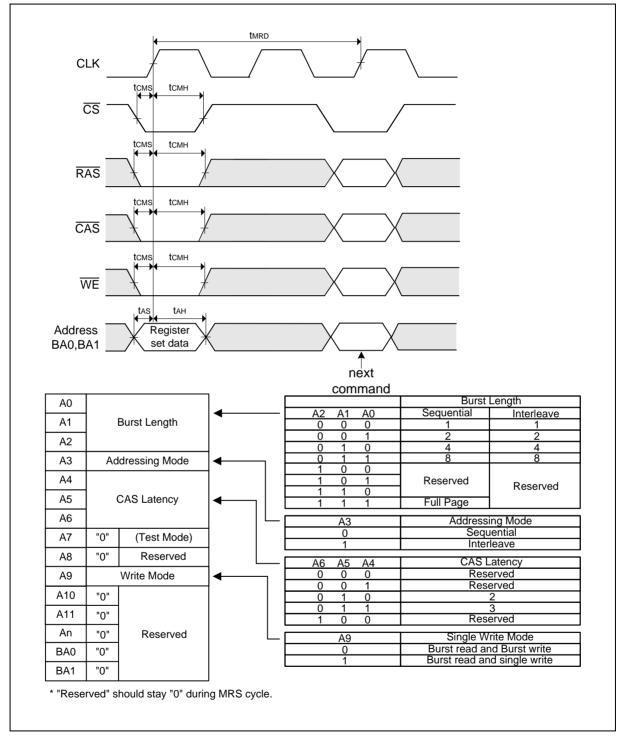

|     | 8.5  |       | Mode Register Operation                                                         | 22   |

|     |      | 8.5.1 | Burst Length field (A2~A0)                                                      | 22   |

|     |      | 8.5.2 | Addressing Mode Select (A3)                                                     |      |

|     |      | 8.5.3 | Addressing Sequence for Sequential Mode                                         |      |

|     |      | 8.5.4 | Addressing Sequence for Interleave Mode                                         |      |

|     |      | 8.5.5 | Addressing Sequence Example (Burst Length = 8 and Input Address is 13)          |      |

|     |      | 8.5.6 | Read Cycle CAS Latency = 3                                                      |      |

|     |      | 8.5.7 | CAS Latency field (A6~A4)                                                       |      |

|     | • •  | 8.5.8 | Mode Register Definition                                                        |      |

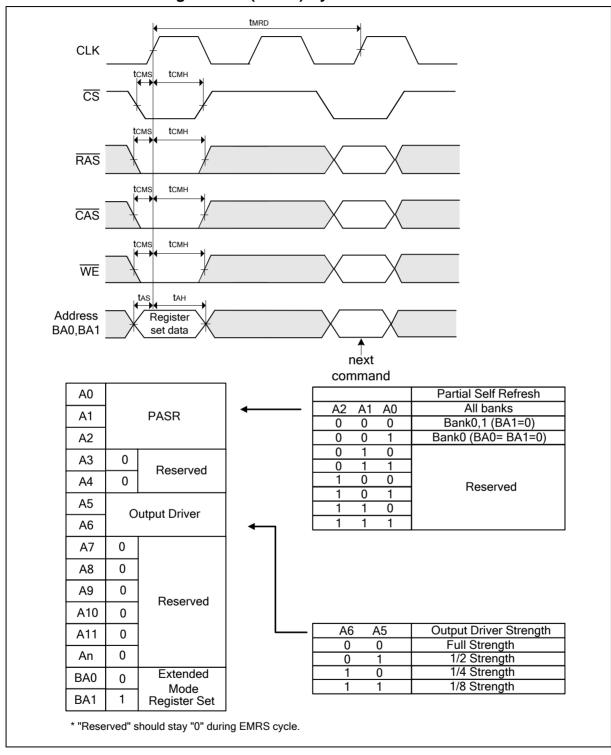

|     | 8.6  |       | Extended Mode Register Description                                              |      |

| 0   | 8.7  | OTOK  | Simplified State Diagram                                                        |      |

| 9.  |      | CIRI  | CAL CHARACTERISTICS                                                             |      |

|     | 9.1  |       | Absolute Maximum Ratings                                                        |      |

|     | 9.2  |       | Operating Conditions                                                            |      |

|     | 9.3  |       | Capacitance                                                                     |      |

|     | 9.4  |       | DC Characteristics                                                              |      |

|     | 9.5  |       | Automatic Temperature Compensated Self Refresh Current Feature                  |      |

|     | 9.6  |       | AC Characteristics and Operating Condition                                      |      |

|     |      | 9.6.1 | AC Characteristics                                                              | -    |

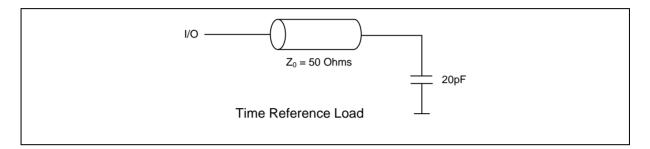

|     |      | 9.6.2 | AC Test Condition                                                               |      |

| 10  |      | 9.6.3 |                                                                                 |      |

| 10. | 40.4 |       |                                                                                 |      |

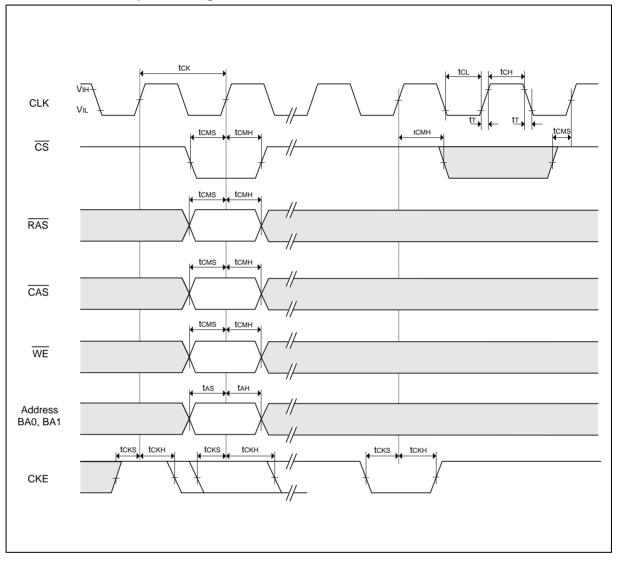

|     | 10.1 |       | Command Input Timing                                                            |      |

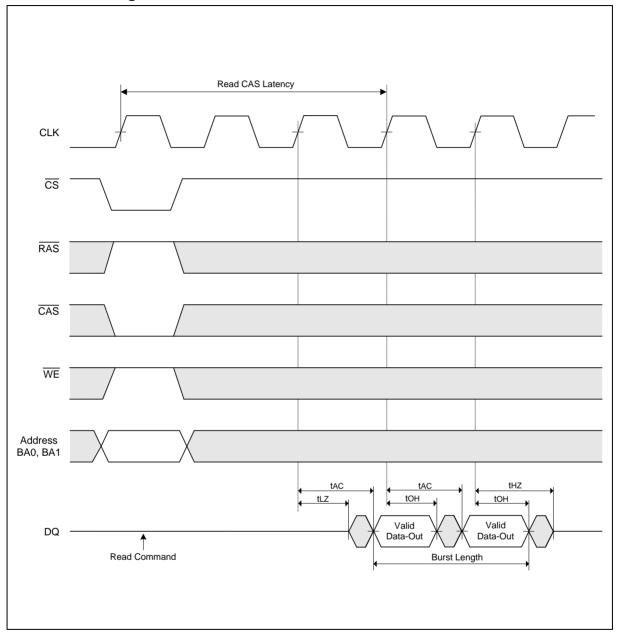

|     | 10.2 |       | Read Timing                                                                     |      |

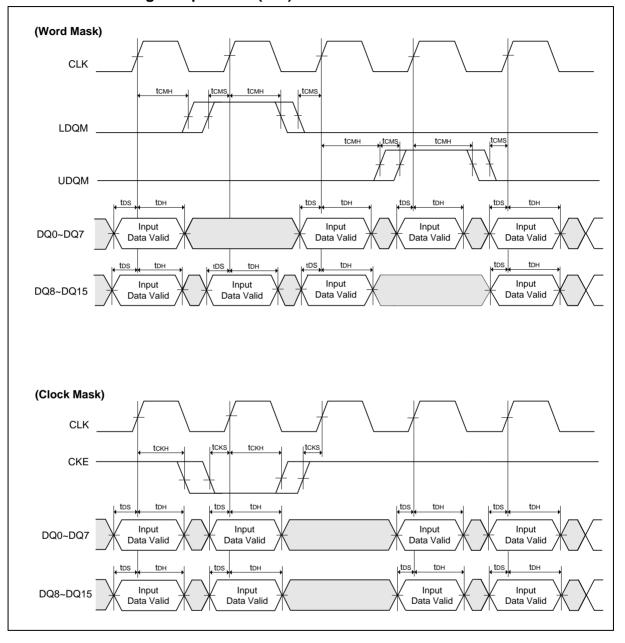

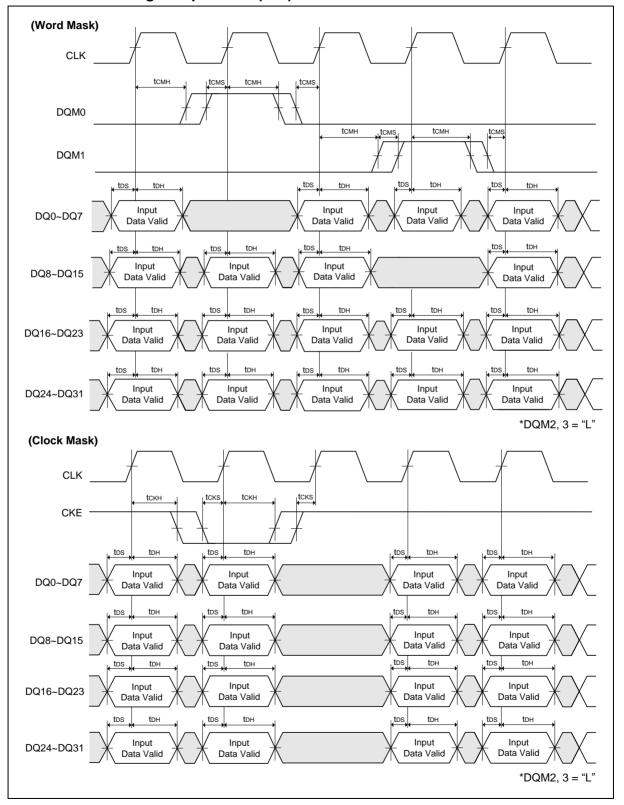

|     | 10.3 |       | Control Timing of Input Data (x16)                                              |      |

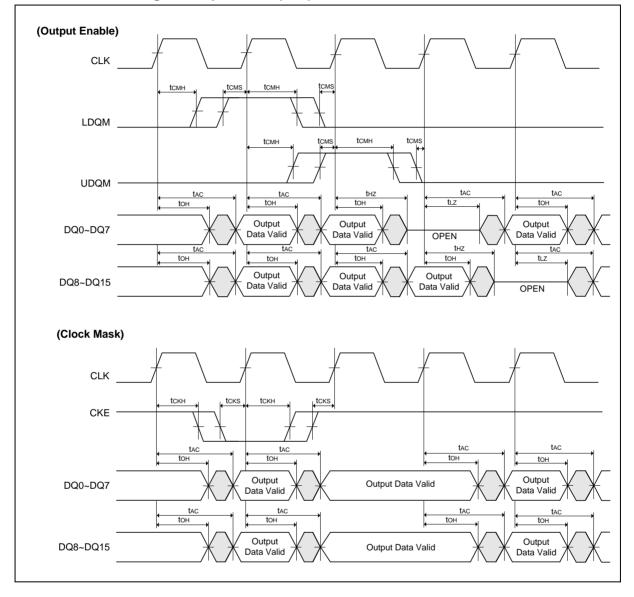

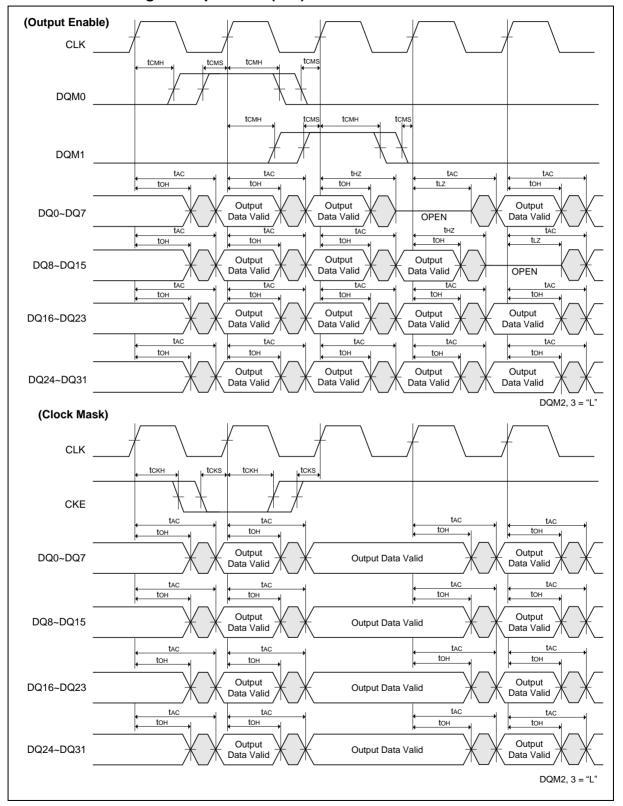

|     | 10.4 |       | Control Timing of Output Data (x16)                                             |      |

|     | 10.5 |       | Control Timing of Input Data (x32)                                              |      |

|     | 10.6 |       | Control Timing of Output Data (x32)                                             |      |

|     | 10.7 |       | Mode Register Set (MRS) Cycle                                                   |      |

|     | 10.8 |       | Extended Mode register Set (EMRS) Cycle                                         |      |

| 11. |      |       |                                                                                 |      |

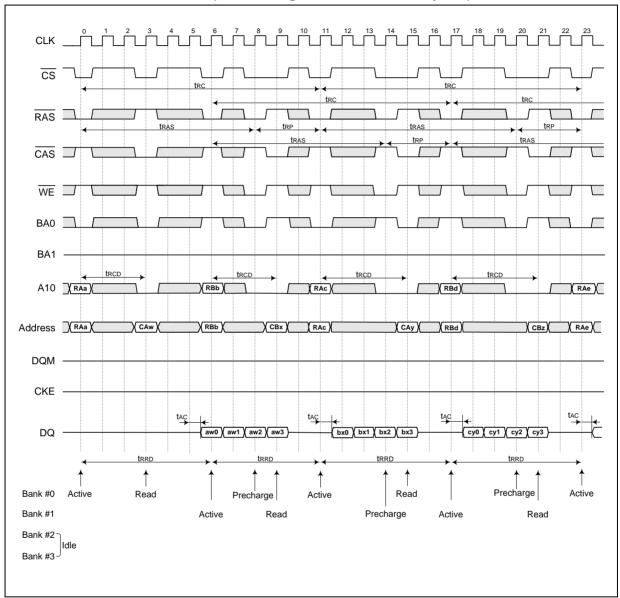

|     | 11.1 |       | Interleaved Bank Read (Burst Length = 4, CAS Latency = 3)                       |      |

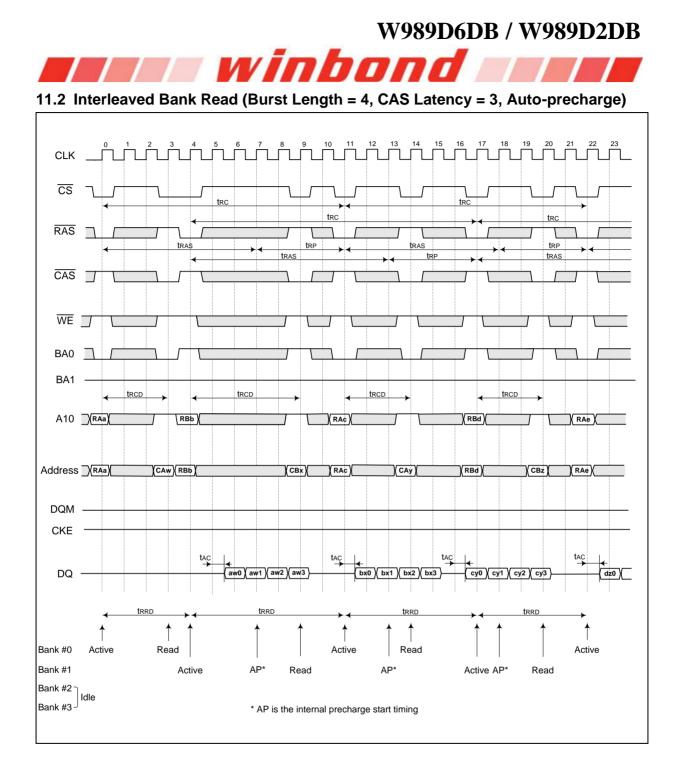

|     | 11.2 |       | Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto-precharge)       |      |

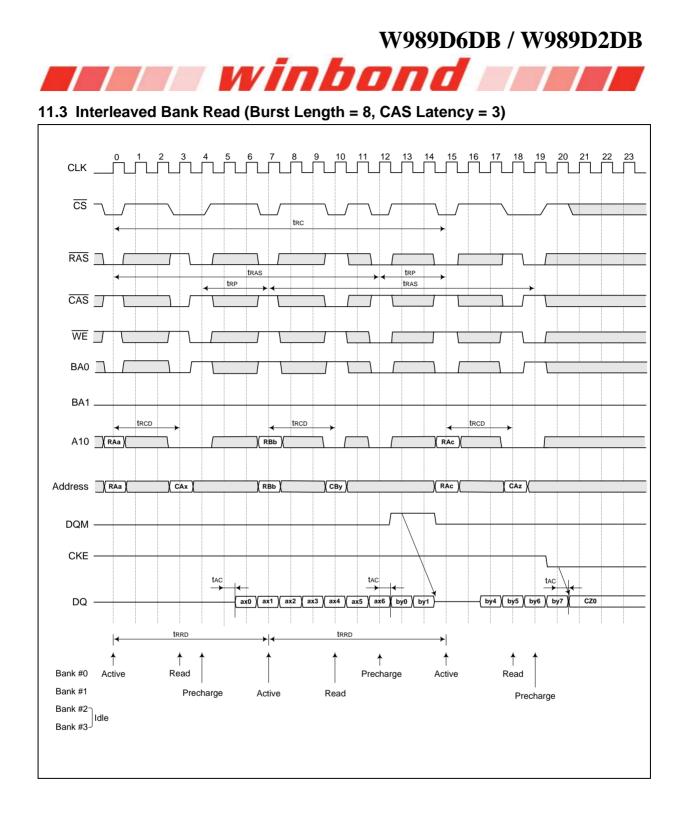

|     | 11.3 |       | Interleaved Bank Read (Burst Length = 8, CAS Latency = 3)                       |      |

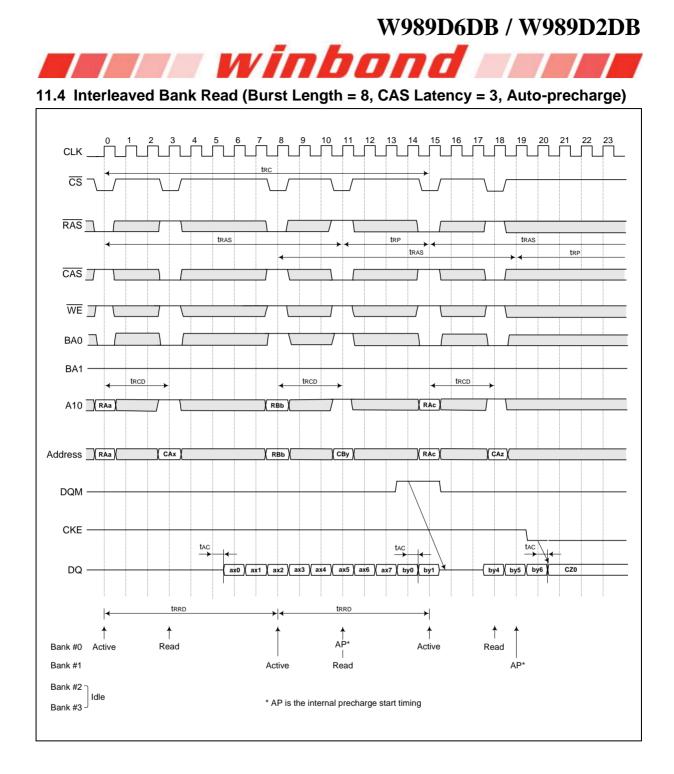

|     | 11.4 |       | Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto-precharge)       |      |

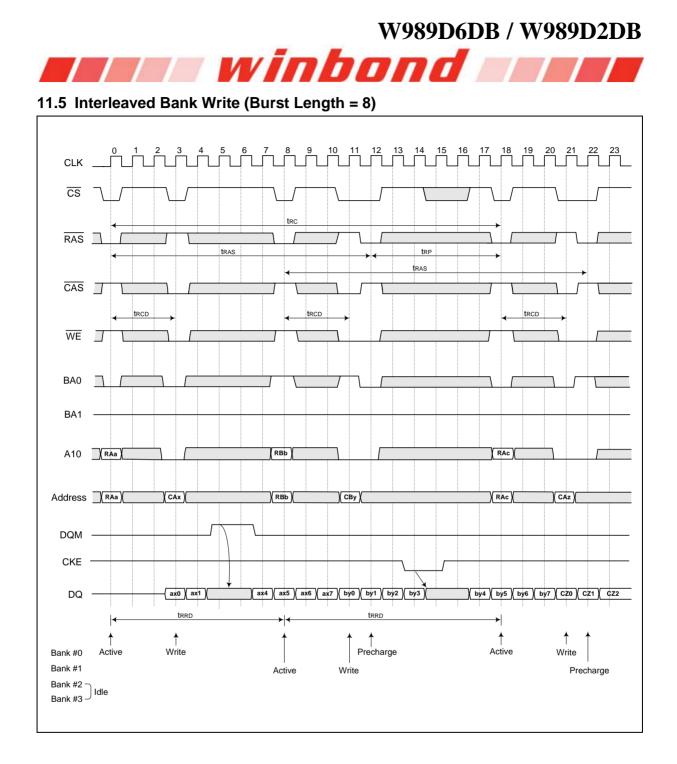

|     | 11.5 |       | Interleaved Bank Write (Burst Length = 8)                                       |      |

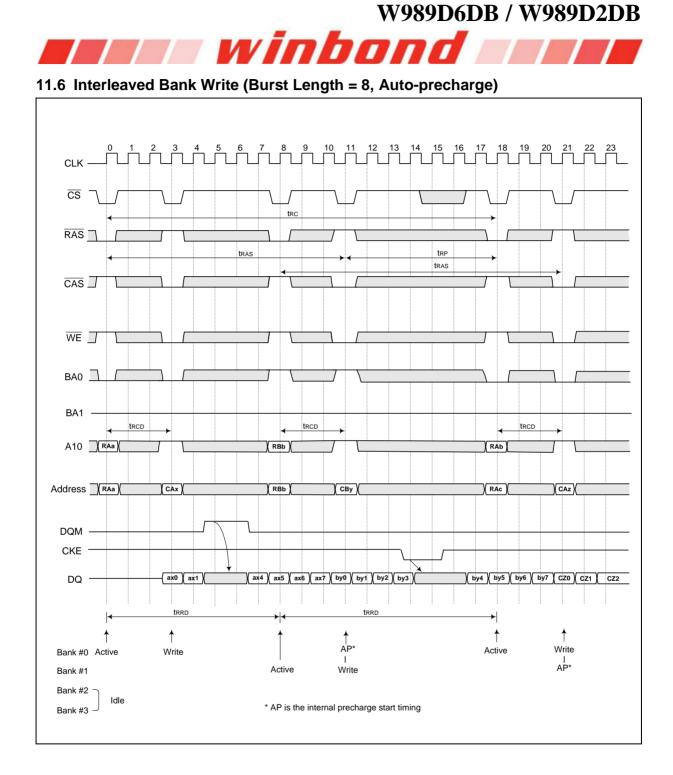

|     | 11.6 |       | Interleaved Bank Write (Burst Length = 8, Auto-precharge)                       |      |

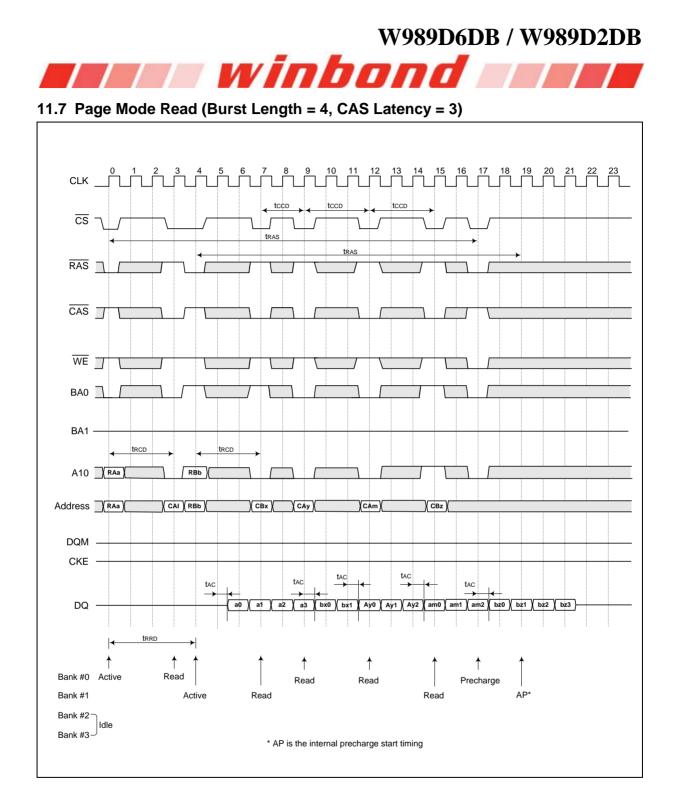

|     | 11.7 |       | Page Mode Read (Burst Length = 4, CAS Latency = 3)                              |      |

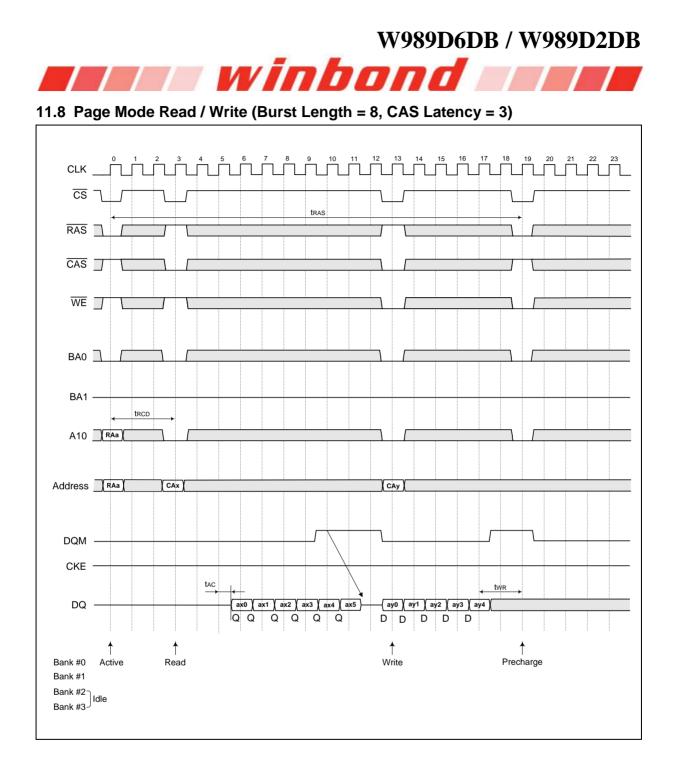

|     | 11.8 |       | Page Mode Read / Write (Burst Length = 8, CAS Latency = 3)                      |      |

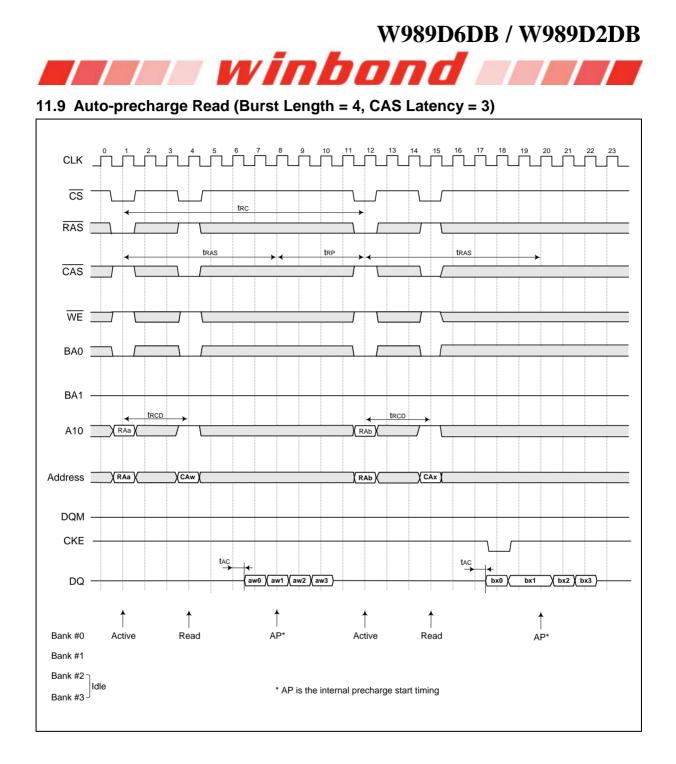

|     | 11.9 |       | Auto-precharge Read (Burst Length = 4, CAS Latency = 3)                         |      |

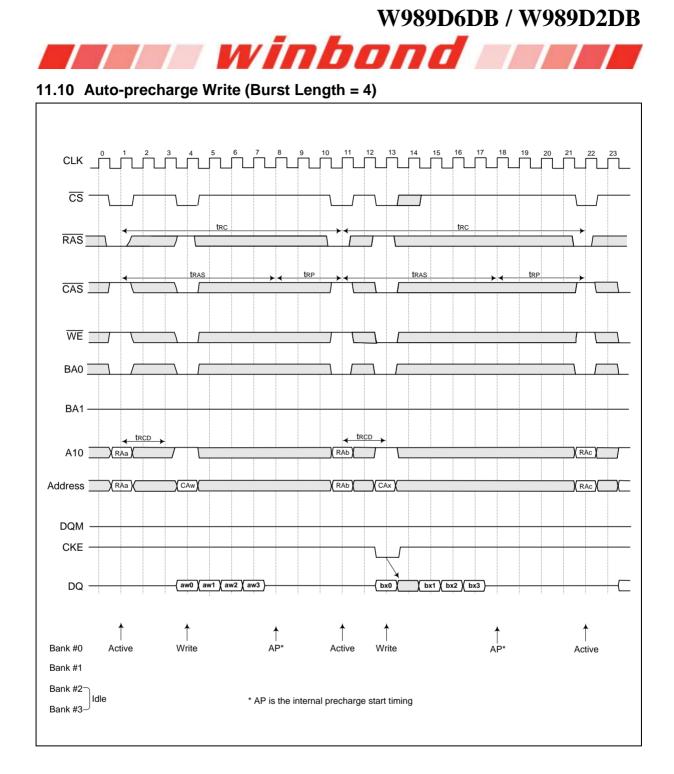

|     | 11.1 |       | Auto-precharge Write (Burst Length = 4)                                         |      |

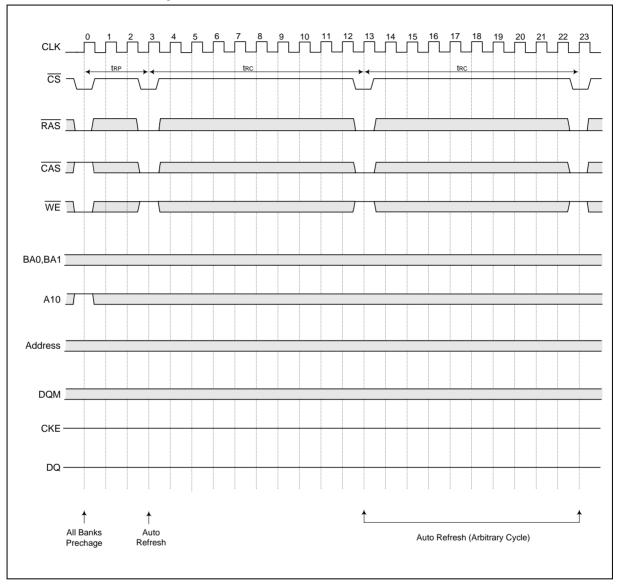

|     | 11.1 | 1     | Auto Refresh Cycle                                                              | 50   |

Publication Release Date: Dec. 01, 2016 Revision: A01-002

|     |       | winbond                                                         |    |

|-----|-------|-----------------------------------------------------------------|----|

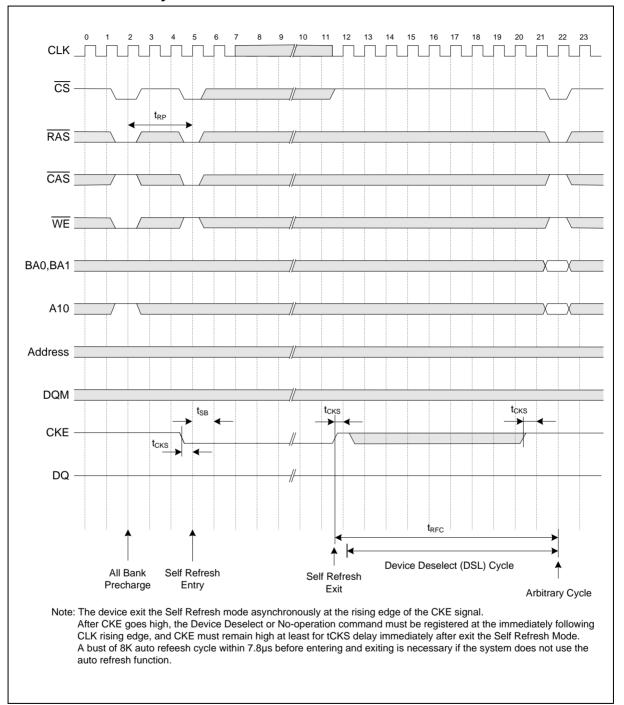

|     | 11.12 | Self Refresh Cycle                                              | 51 |

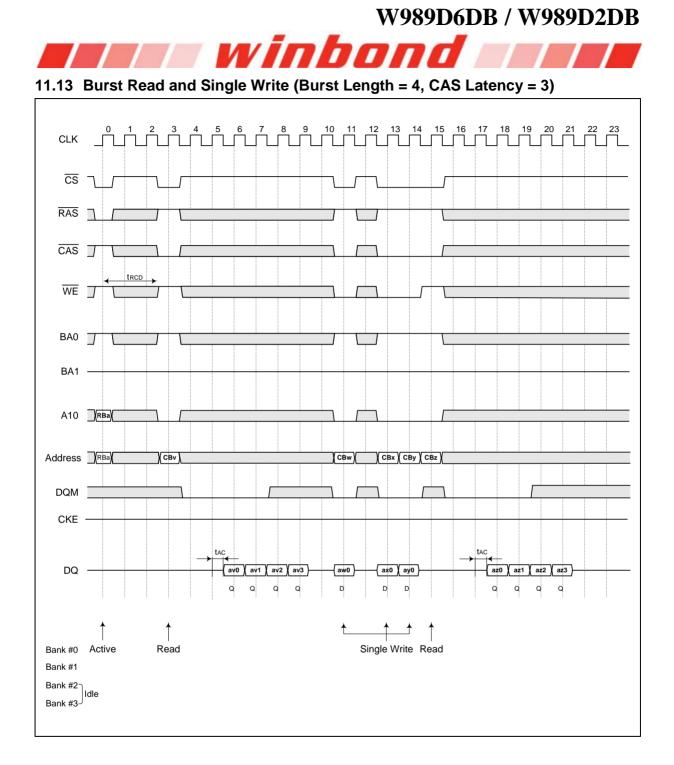

|     | 11.13 | Burst Read and Single Write (Burst Length = 4, CAS Latency = 3) | 52 |

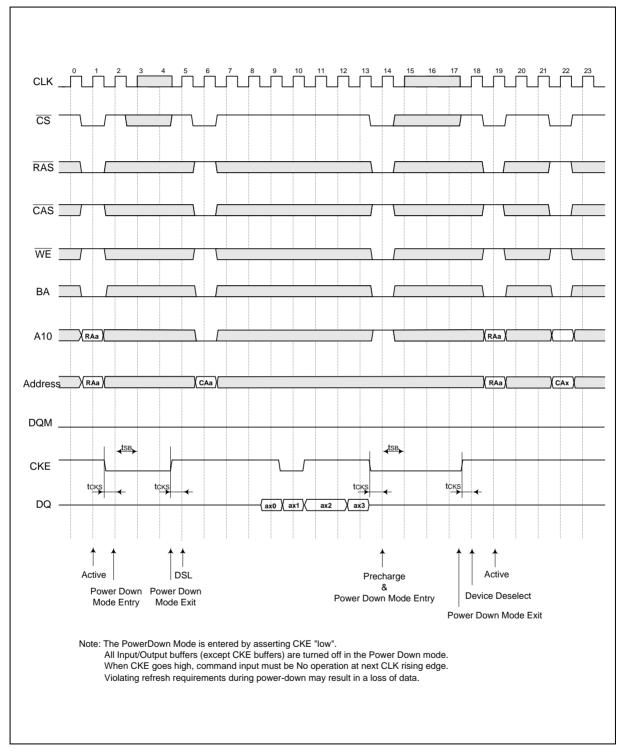

|     | 11.14 | Power Down Mode                                                 | 53 |

|     | 11.15 | Deep Power Down Mode Entry                                      | 54 |

|     | 11.16 | Deep Power Down Mode Exit                                       | 55 |

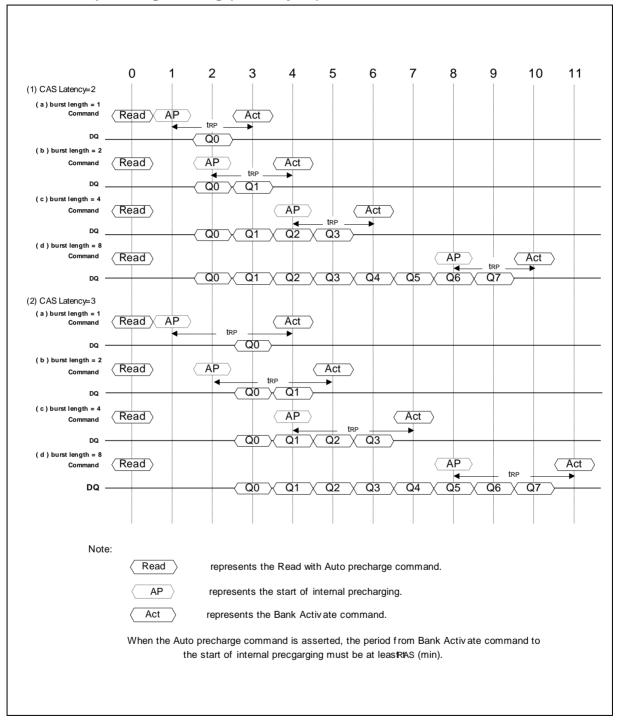

|     | 11.17 | Auto-precharge Timing (Read Cycle)                              | 56 |

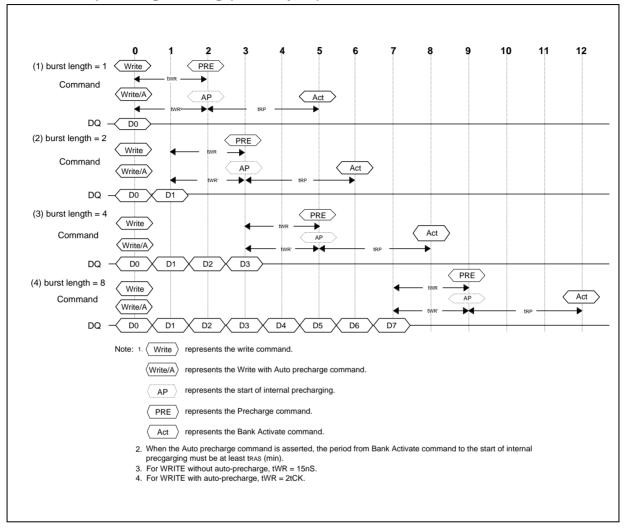

|     | 11.18 | Auto-precharge Timing (Write Cycle)                             | 57 |

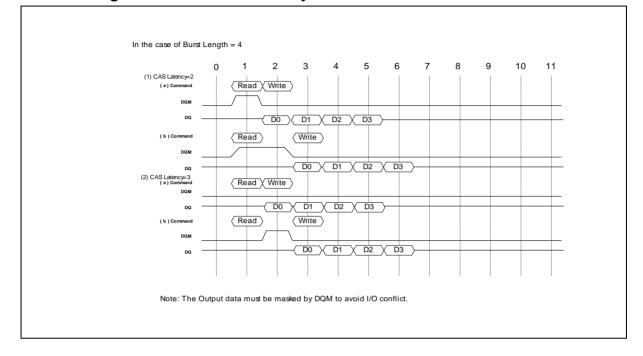

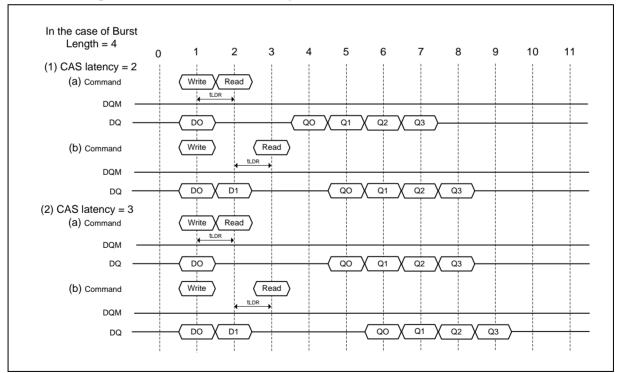

|     | 11.19 | Timing Chart of Read to Write Cycle                             | 58 |

|     | 11.20 | Timing Chart of Write to Read Cycle                             | 58 |

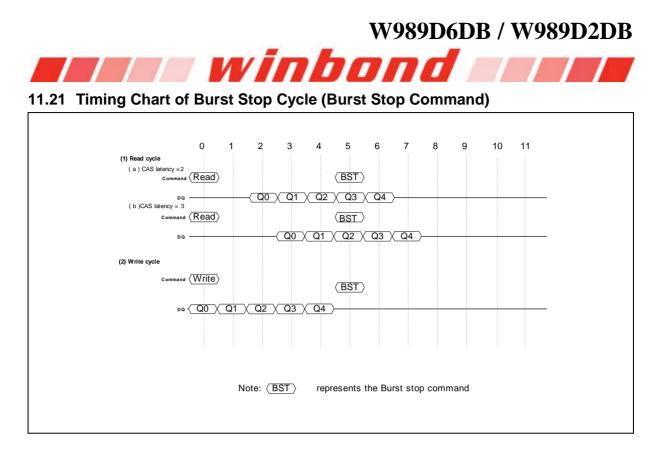

|     | 11.21 | Timing Chart of Burst Stop Cycle (Burst Stop Command)           | 59 |

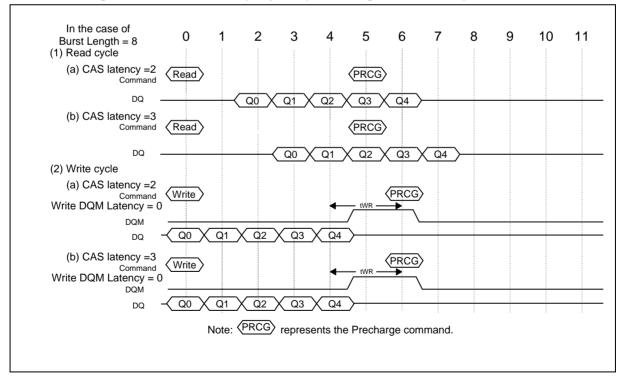

|     | 11.22 | Timing Chart of Burst Stop Cycle (Precharge Command)            | 59 |

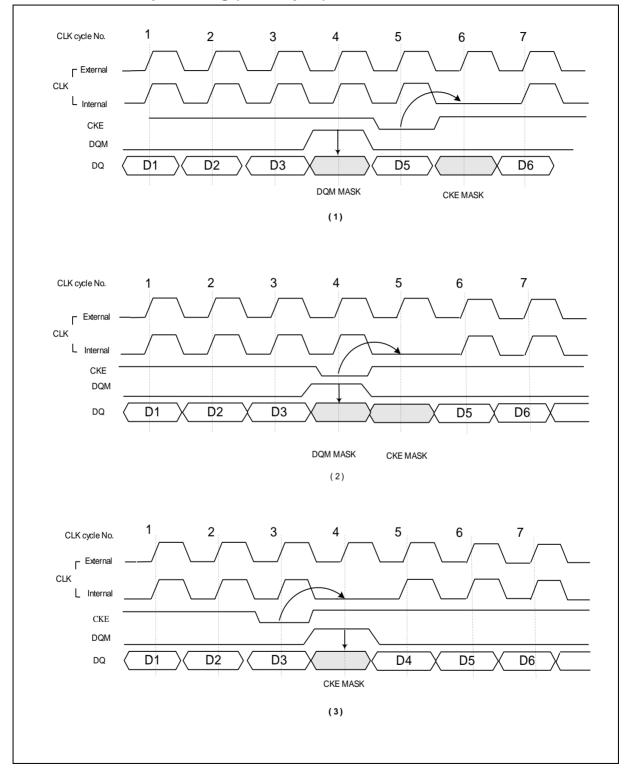

|     | 11.23 | CKE/DQM Input Timing (Write Cycle)                              | 60 |

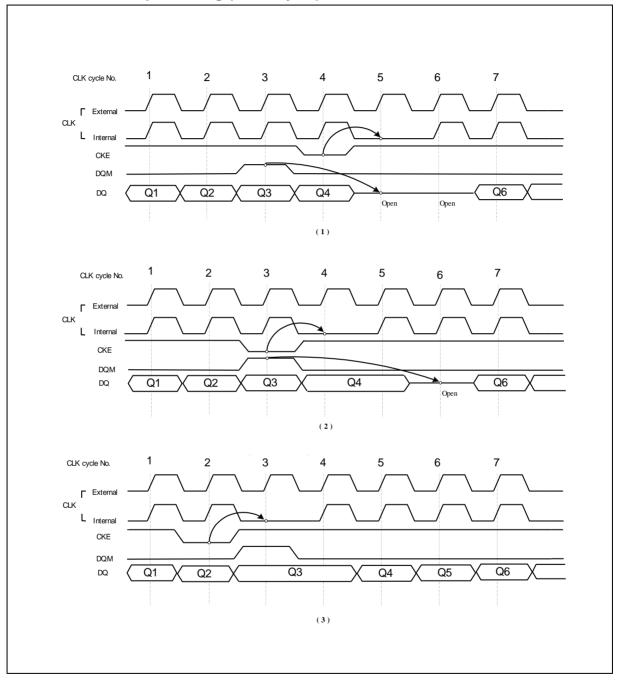

|     | 11.24 | CKE/DQM Input Timing (Read Cycle)                               | 61 |

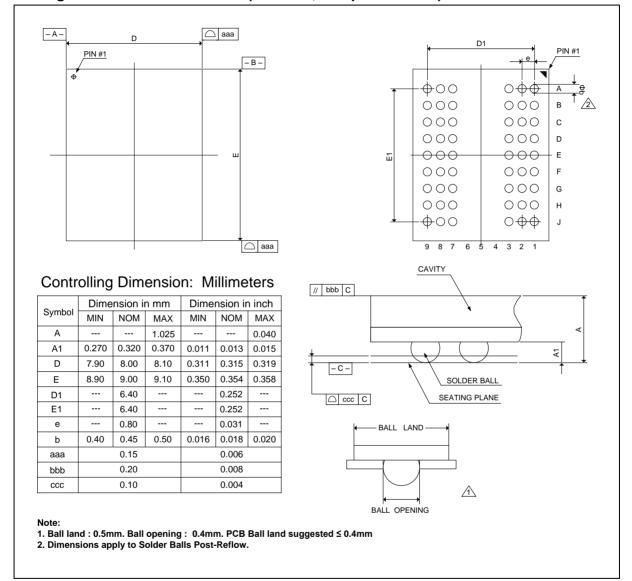

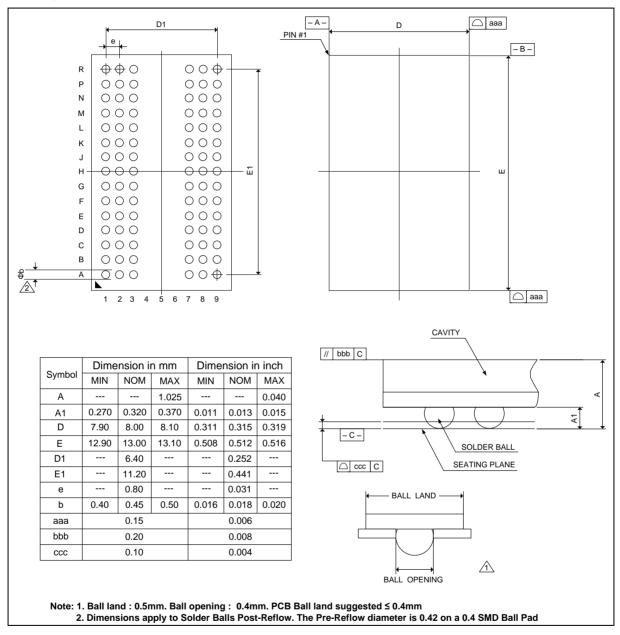

| 12. | PAC   | KAGE SPECIFICATION                                              | 62 |

|     | 12.1  | LPSDR x16                                                       |    |

|     | 12.2  | LPSDR x32                                                       | 63 |

| 13. | REVI  | SION HISTORY                                                    | 64 |

# **FEESE Winbond**

# 1. GENERAL DESCRIPTION

The Winbond 512Mb Low Power SDRAM is a low power synchronous memory containing 536,870,912 memory cells fabricated with Winbond high performance process technology.

It is designed to consume less power than the ordinary SDRAM with low power features essential for applications which use batteries. It is available in two organizations: 4,194,304 words × 4 banks × 32 bits or 8,388,608 words × 4 banks × 16 bits. The device operates in a fully synchronous mode, and the output data are synchronized to positive edges of the system clock and is capable of delivering data at clock rate up to 166MHz. The device supports special low power functions such as Partial Array Self Refresh (PASR) and Automatic Temperature Compensated Self Refresh (ATCSR).

The Low Power SDRAM is suitable for 2.5G / 3G cellular phone, PDA, digital still camera, mobile game consoles and other handheld applications where large memory density and low power consumption are required. The device operates from 1.8V power supply, and supports the 1.8V LVCMOS bus interface.

# 2. FEATURES

- Power supply VDD = 1.7V~1.95V

- VDDQ = 1.7V~1.95V

- Frequency: 166MHz(-6)

- Standard Self Refresh Mode

- Programmable Partial Array Self Refresh

- Power Down Mode

- Deep Power Down Mode (DPD)

- Programmable output buffer driver strength

- Automatic Temperature Compensated Self Refresh

- CAS Latency: 2 and 3

- Burst Length: 1, 2, 4, 8, and full page

- Refresh: 8K refresh cycle / 64mS

- Interface: LVCMOS

- Support package: 54 balls VFBGA (x16) 90 balls VFBGA (x32)

- Operating Temperature Range: Extended (-25°C ~ +85°C) Industrial (-40°C ~ +85°C)

# 3. ORDER INFORMATION

| Part Number  | VDD/VDDQ  | I/O Width | Package        | Others             |

|--------------|-----------|-----------|----------------|--------------------|

| W989D6DBGX6I | 1.8V/1.8V | 16        | 54 balls VFBGA | 166MHz, -40°C~85°C |

| W989D6DBGX6E | 1.8V/1.8V | 16        | 54 balls VFBGA | 166MHz, -25°C~85°C |

| W989D2DBJX6I | 1.8V/1.8V | 32        | 90 balls VFBGA | 166MHz, -40°C~85°C |

| W989D2DBJX6E | 1.8V/1.8V | 32        | 90 balls VFBGA | 166MHz, -25°C~85°C |

4. BALL CONFIGURATION

4.1 Ball Assignment: LPSDR x16

|   |            |            |            | То | o View | / |            |            |            |

|---|------------|------------|------------|----|--------|---|------------|------------|------------|

|   | 1          | 2          | 3          | 4  | 5      | 6 | 7          | 8          | 9          |

|   |            |            |            |    |        |   |            |            |            |

| A | ()<br>Vss  | ()<br>DQ15 | ()<br>Vssq |    |        |   |            |            | VDD        |

| 3 | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |    |        |   | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

| c | DQ14       | DQ13       |            |    |        |   | VSSQ       | DQ2        | DQ1        |

| 5 | DQ12       | DQ11       | VSSQ       |    |        |   |            | DQ4        | DQ3        |

|   | DQ10       | DQ9        | VDDQ       |    |        |   | Vssq       | DQ6        | DQ5        |

| E | DQ8        | O<br>NC    | ⊖<br>Vss   |    |        |   |            |            | DQ7        |

| F | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |    |        |   |            |            |            |

| G |            |            | CKE        |    |        |   | /CAS       | /RAS       | /WE        |

| н | A12        | A11        | A9         |    |        |   | BA0        | BA1        | /CS        |

|   | A8         | A7         | A6         |    |        |   | A0         | A1         | A10        |

| J | Uss        | ()<br>A5   | ()<br>A4   |    |        |   | ()<br>A3   | ()<br>A2   |            |

|   | 100        | 710        |            |    |        |   |            |            |            |

4.2 Ball Assignment: LPSDR x32

|   |            |            |            | То | p Vie | ew |            |            |            |

|---|------------|------------|------------|----|-------|----|------------|------------|------------|

|   | 1          | 2          | 3          | 4  | 5     | 6  | 7          | 8          | 9          |

| A |            | O<br>DQ24  |            |    |       |    |            | O<br>DQ23  | O<br>DQ21  |

| в | DQ26       | $\bigcirc$ | Vss        |    |       |    |            | $\bigcirc$ | $\bigcirc$ |

| С | DQ28       | VDDQ       | Vssq       |    |       |    |            | Vssq       | DQ19       |

| D | Vssq       | DQ27       | DQ25       |    |       |    | DQ22       | DQ20       |            |

| E | VSSQ       | DQ29       |            |    |       |    | DQ17       | DQ18       |            |

|   | VDDQ       | DQ31       | NC         |    |       |    | NC         | DQ16       | Vssq       |

| F | vss        |            | A3         |    |       |    | A2         | DQM2       |            |

| G | ()<br>A4   | ()<br>A5   | (<br>A6    |    |       |    | ()<br>A10  | ()<br>A0   | (<br>A1    |

| Н | ⊖<br>A7    | 0<br>A8    | ()<br>A12  |    |       |    |            | O<br>BA1   | O<br>A11   |

| J |            | СКЕ        | ()<br>A9   |    |       |    | O<br>BA0   | )<br>/CS   | )<br>/RAS  |

| к | DQM1       |            |            |    |       |    | )<br>/CAS  | )<br>/WE   | DQM0       |

| L | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |    |       |    | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

| м |            | DQ8        | Vss        |    |       |    | VDD        | DQ7        | VSSQ       |

| N | VSSQ       |            | DQ9        |    |       |    | DQ6        | DQ5        |            |

|   | $\frown$   | DQ12       | $\frown$   |    |       |    | DQ1        | DQ3        |            |

| P | DQ11       | VDDQ       | VSSQ       |    |       |    | VDDQ       | Vssq       | DQ4        |

| R | DQ13       | DQ15       | Vss        |    |       |    |            |            | DQ2        |

# 5. BALL DESCRIPTION

# 5.1 Signal Description

| Ball Name                           | Function                 | Description                                                                                                                                                                                    |

|-------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A [n:0]                             | Address                  | Multiplexed pins for row and column address.<br>A10 is Auto Precharge Select                                                                                                                   |

| BA0, BA1                            | Bank Select              | Select bank to activate during row address latch time, or bank to read/write during address latch time.                                                                                        |

| DQ0~DQ15 (×16)<br>DQ0~DQ31 (×32)    | Data Input/ Output       | Multiplexed pins for data output and input.                                                                                                                                                    |

| CS                                  | Chip Select              | Disable or enable the command decoder. When<br>command decoder is disabled, new command is ignored<br>and previous operation continues.                                                        |

| RAS                                 | Row Address<br>Strobe    | Command input. When sampled at the rising edge of the clock, $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ and $\overline{\text{WE}}$ define the operation to be executed.                 |

| CAS                                 | Column Address<br>Strobe | Referred to RAS                                                                                                                                                                                |

| WE                                  | Write Enable             | Referred to WE                                                                                                                                                                                 |

| UDQM / LDQM(x16)<br>DQM0~DQM3 (x32) | I/O Mask                 | The output buffer is placed at Hi-Z (with latency of 2 in CL=2, 3;) when DQM is sampled high in read cycle. In write cycle, sampling DQM high will block the write operation with zero latency |

| CLK                                 | Clock Inputs             | System clock used to sample inputs on the rising edge of clock.                                                                                                                                |

| СКЕ                                 | Clock Enable             | CKE controls the clock activation and deactivation. When CKE is low, Power Down mode, Suspend mode or Self Refresh mode is entered.                                                            |

| VDD                                 | Power                    | Power supply for input buffers and logic circuit inside DRAM.                                                                                                                                  |

| VSS                                 | Ground                   | Ground for input buffers and logic circuit inside DRAM.                                                                                                                                        |

| VDDQ                                | Power for I/O Buffer     | Power supply separated from VDD, used for output buffers to improve noise.                                                                                                                     |

| VSSQ                                | Ground for I/O<br>Buffer | Separated ground from VSS, used for output buffers to improve noise.                                                                                                                           |

| NC                                  | No Connection            | No connection                                                                                                                                                                                  |

# 5.2 Addressing Table

| li li    | tem              | 512 Mb  |  |  |  |

|----------|------------------|---------|--|--|--|

| Numbe    | r of banks       | 4       |  |  |  |

| Bank ac  | ldress pins      | BA0,BA1 |  |  |  |

| Auto pre | charge pin       | A10/AP  |  |  |  |

| Т        | уре              | Package |  |  |  |

| x16      | Row addresses    | A0-A12  |  |  |  |

| XIO      | Column addresses | A0-A9   |  |  |  |

| x32      | Row addresses    | A0-A12  |  |  |  |

| X32      | Column addresses | A0-A8   |  |  |  |

1

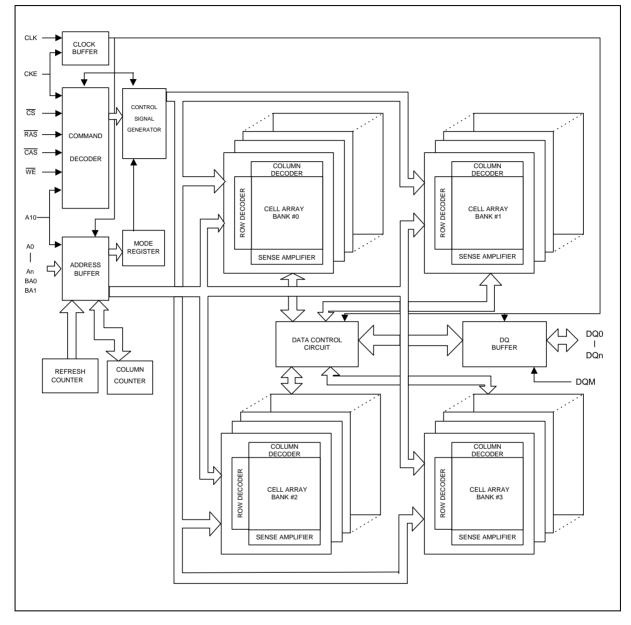

# 6. BLOCK DIAGRAM

# 7. FUNCTIONAL DESCRIPTION

### 7.1 Command Function

## 7.1.1 Table 1. Truth Table (Note (1) and (2))

| Symbol | Command                       | Device State               | CKEn-1 | CKEn | DQM <sup>(5)</sup> | BA0, 1 | A10 | A0-An | cs | RAS    | CAS    | WE     |

|--------|-------------------------------|----------------------------|--------|------|--------------------|--------|-----|-------|----|--------|--------|--------|

| ACT    | Bank Activate                 | Idle <sup>(3)</sup>        | Н      | Х    | Х                  | V      | V   | V     | L  | L      | Н      | Н      |

| PRE    | Bank Precharge                | Any                        | Н      | Х    | Х                  | V      | L   | Х     | L  | L      | Н      | L      |

| PREA   | Precharge All                 | Any                        | Н      | Х    | Х                  | Х      | Н   | х     | L  | L      | Н      | L      |

| WRIT   | Write                         | Active <sup>(3)</sup>      | Н      | Х    | Х                  | V      | L   | V     | L  | Н      | L      | L      |

| WRITA  | Write with Auto<br>Precharge  | Active <sup>(3)</sup>      | н      | х    | х                  | V      | Н   | V     | L  | н      | L      | L      |

| READ   | Read                          | Active <sup>(3)</sup>      | Н      | Х    | Х                  | V      | L   | V     | L  | Н      | L      | Н      |

| READA  | Read with Auto<br>Precharge   | Active <sup>(3)</sup>      | н      | х    | х                  | V      | Н   | V     | L  | н      | L      | Н      |

| MRS    | Mode Register Set             | Idle                       | Н      | Х    | Х                  | V      | V   | V     | L  | L      | L      | L      |

| EMRS   | Extended Mode<br>Register Set | Idle                       | н      | х    | х                  | V      | V   | V     | L  | L      | L      | L      |

| NOP    | No-Operation                  | Any                        | Н      | Х    | Х                  | Х      | Х   | х     | L  | Н      | Н      | Н      |

| BST    | Burst stop                    | Active <sup>(4)</sup>      | Н      | Х    | Х                  | Х      | Х   | Х     | L  | Н      | Н      | L      |

| DSL    | Device Deselect               | Any                        | Н      | Х    | Х                  | Х      | Х   | Х     | Н  | Х      | Х      | Х      |

| AREF   | Auto-Refresh                  | Idle                       | Н      | Н    | Х                  | Х      | Х   | Х     | L  | L      | L      | Н      |

| SELF   | Self-Refresh Entry            | ldle                       | Н      | L    | Х                  | Х      | х   | Х     | L  | L      | L      | Н      |

| SELEX  | Self-Refresh Exit             | ldle<br>(Self Refresh)     | L      | н    | х                  | х      | х   | х     | H  | Х<br>Н | Х<br>Н | X<br>H |

| CSE    | Clock Suspend<br>Mode Entry   | Active                     | н      | L    | х                  | х      | х   | х     | х  | х      | х      | х      |

| PD     | Power Down Mode<br>Entry      | Idle/Active <sup>(6)</sup> | н      | L    | х                  | х      | х   | х     | H  | Х<br>Н | X<br>H | X<br>H |

| CSEX   | Clock Suspend<br>Mode Exit    | Active                     | L      | н    | х                  | х      | х   | х     | х  | х      | х      | х      |

| DDEX   | Power Down Mode               | Any                        |        |      | Ň                  | v      | v   | X     | Н  | Х      | Х      | Х      |

| PDEX   | Exit                          | (Power Down)               | L      | Н    | X                  | Х      | Х   | Х     | L  | Н      | Н      | Х      |

| DE     | Data Write/Output<br>Enable   | Active                     | н      | х    | L                  | х      | х   | х     | х  | х      | х      | х      |

| DD     | Data Write/Output<br>Disable  | Active                     | н      | х    | н                  | х      | х   | х     | х  | х      | х      | х      |

| DPD    | Deep Power Down<br>Mode Entry | Idle                       | н      | L    | х                  | х      | х   | х     | L  | н      | н      | L      |

| DPDE   | Deep Power Down<br>Mode Exit  | Idle (DPD)                 | L      | Н    | х                  | х      | х   | Х     | х  | х      | х      | х      |

#### Notes:

(1) v = valid, x = Don't care, L = Low Level, H = High Level

(2) CKEn signal is input level when commands are provided.

CKEn-1 signal is the input level one clock cycle before the command is issued.

(3) These are state of bank designated by BA0, BA1 signals.

- (4) Device state is full page burst operation.

- (5) x32: DQM0-3, x16 : LDQM / UDQM

(6) Power Down Mode can not be entered in the burst cycle.

When this command asserts in the burst cycle, device state is clock suspend mode.

# 7.1.2 Functional Truth Table (See Note 1)

| Current<br>State | cs | RAS | CAS | WE | Address     | Command    | Action                                   | Notes |

|------------------|----|-----|-----|----|-------------|------------|------------------------------------------|-------|

|                  | Н  | Х   | Х   | Х  | Х           | DSL        | Nop                                      |       |

|                  | L  | Н   | Н   | Х  | Х           | NOP/BST    | Nop                                      |       |

|                  | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA | ILLEGAL                                  | 3     |

| Idle             | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                                  | 3     |

| luie             | L  | L   | Н   | Н  | BA, RA      | ACT        | Row activating                           |       |

|                  | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | Nop                                      |       |

|                  | L  | L   | L   | Н  | Х           | AREF/SELF  | Refresh or Self refresh                  | 2     |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | Mode register accessing                  | 2     |

|                  | Н  | Х   | Х   | Х  | Х           | DSL        | Nop                                      |       |

|                  | L  | Н   | Н   | Х  | Х           | NOP/BST    | Nop                                      |       |

|                  | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA | Begin read: Determine AP                 | 4     |

| Deve estive      | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | Begin write: Determine AP                | 4     |

| Row active       | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                                  | 3     |

|                  | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | Precharge                                | 5     |

|                  | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                                  |       |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                                  |       |

|                  | Н  | Х   | Х   | Х  | Х           | DSL        | Continue burst to end                    |       |

| _                | L  | Н   | н   | Н  | Х           | NOP        | Continue burst to end                    |       |

|                  | L  | Н   | Н   | L  | Х           | BST        | Burst stop                               |       |

|                  | L  | н   | L   | Н  | BA, CA, A10 | READ/READA | Term burst, new read: Determine AP       | 6     |

| Read             | L  | н   | L   | L  | BA, CA, A10 | WRIT/WRITA | Term burst, begin write:<br>Determine AP | 6, 7  |

|                  | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                                  | 3     |

|                  | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | Term burst, precharging                  |       |

|                  | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                                  |       |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                                  |       |

|                  | Н  | Х   | Х   | Х  | Х           | DSL        | Continue burst to end.                   |       |

|                  | L  | Н   | н   | Н  | Х           | NOP        | Continue burst to end                    |       |

|                  | L  | н   | н   | L  | х           | BST        | Burst stop, row active                   |       |

|                  | L  | н   | L   | н  | BA, CA, A10 | READ/READA | Term burst, start read: Determine AP     | 6, 7  |

| Write            | L  | н   | L   | L  | BA, CA, A10 | WRIT/WRITA | Term burst, new write: Determine<br>AP   | 6     |

|                  | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                                  | 3     |

|                  | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | Term burst. precharging                  | 8     |

|                  | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                                  |       |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                                  |       |

|                   |    |     |     |    | inb         |            |                                                     |       |

|-------------------|----|-----|-----|----|-------------|------------|-----------------------------------------------------|-------|

| Current<br>State  | cs | RAS | CAS | WE | Address     | Command    | Action                                              | Notes |

|                   | Н  | Х   | Х   | Х  | Х           | DSL        | Continue burst to end                               |       |

|                   | L  | Н   | Н   | Н  | Х           | NOP        | Continue burst to end                               |       |

|                   | L  | Н   | Н   | L  | х           | BST        | ILLEGAL                                             |       |

| Read with         | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA | ILLEGAL                                             | 3     |

| auto              | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                                             | 3     |

| precharge         | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                                             | 3     |

|                   | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | ILLEGAL                                             | 3     |

|                   | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                                             |       |

|                   | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                                             |       |

|                   | Н  | Х   | Х   | Х  | Х           | DSL        | Continue burst to end                               |       |

|                   | L  | Н   | Н   | Н  | Х           | NOP        | Continue burst to end                               |       |

|                   | L  | Н   | Н   | L  | Х           | BST        | ILLEGAL                                             | -     |

| Write with        | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA | ILLEGAL                                             | 3     |

| auto              | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                                             | 3     |

| precharge         | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                                             | 3     |

|                   | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | ILLEGAL                                             | 3     |

|                   | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                                             | -     |

|                   | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                                             |       |

|                   | Н  | Х   | Х   | Х  | Х           | DSL        | Nop $\rightarrow$ Idle after t <sub>RP</sub>        |       |

|                   | L  | Н   | Н   | Н  | х           | NOP        | Nop $\rightarrow$ Idle after t <sub>RP</sub>        |       |

|                   | L  | Н   | Н   | L  | х           | BST        | ILLEGAL                                             | -     |

|                   | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA | ILLEGAL                                             | 3     |

| Precharging       | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                                             | 3     |

|                   | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                                             | 3     |

|                   | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | Nop $\rightarrow$ Idle after t <sub>RP</sub>        |       |

|                   | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                                             | -     |

|                   | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                                             | -     |

|                   | Н  | Х   | Х   | Х  | Х           | DSL        | Nop $\rightarrow$ Row active after t <sub>RCD</sub> |       |

|                   | L  | Н   | Н   | Н  | Х           | NOP        | Nop $\rightarrow$ Row active after t <sub>RCD</sub> |       |

|                   | L  | Н   | Н   | L  | Х           | BST        | ILLEGAL                                             |       |

|                   | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA | ILLEGAL                                             | 3     |

| Row<br>activating | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                                             | 3     |

| Ĵ                 | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                                             | 3     |

|                   | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | ILLEGAL                                             | 3     |

|                   | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                                             |       |

|                   | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                                             |       |

\_\_\_\_

|                       |    |     |     |    |             | 001                                      |                                                             |       |

|-----------------------|----|-----|-----|----|-------------|------------------------------------------|-------------------------------------------------------------|-------|

| Current<br>State      | cs | RAS | CAS | WE | Address     | Command                                  | Action                                                      | Notes |

|                       | Н  | Х   | Х   | Х  | Х           | DSL                                      | Nop $\rightarrow$ Maintain Row active after twR             |       |

|                       | L  | Н   | Н   | Н  | Х           | NOP                                      | Nop $\rightarrow$ Maintain Row active after t <sub>WR</sub> |       |

|                       | L  | Н   | Н   | L  | Х           | BST                                      | Nop $\rightarrow$ Maintain Row active after twR             |       |

|                       | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA                               | Begin Read                                                  | 7     |

| Write<br>recovering   | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA                               | Begin new Write                                             |       |

| 0                     | L  | L   | Н   | Н  | BA, RA      | ACT                                      | ILLEGAL                                                     | 3     |

|                       | L  | L   | Н   | L  | BA, A10     | PRE/PREA                                 | ILLEGAL                                                     | 3     |

|                       | L  | L   | L   | Н  | Х           | AREF/SELF                                | ILLEGAL                                                     |       |

|                       | L  | L   | L   | L  | Op-Code     | MRS/EMRS                                 | ILLEGAL                                                     |       |

|                       | Н  | Х   | Х   | Х  | Х           | DSL                                      | Nop $\rightarrow$ Enter precharge after t <sub>WR</sub>     |       |

|                       | L  | Н   | Н   | Н  | Х           | NOP                                      | Nop $\rightarrow$ Enter precharge after twR                 |       |

|                       | L  | Н   | Н   | L  | Х           | BST                                      | Nop $\rightarrow$ Enter precharge after twR                 |       |

| Write                 | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA                               | ILLEGAL                                                     | 3     |

| recovering with auto  | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA                               | ILLEGAL                                                     | 3     |

| precharge             | L  | L   | Н   | Н  | BA, RA      | ACT                                      | ILLEGAL                                                     | 3     |

|                       | L  | L   | Н   | L  | BA, A10     | PRE/PREA                                 | ILLEGAL                                                     | 3     |

|                       | L  | L   | L   | Н  | Х           | AREF/SELF                                | ILLEGAL                                                     |       |

|                       | L  | L   | L   | L  | Op-Code     | MRS/EMRS                                 | ILLEGAL                                                     |       |

|                       | Н  | Х   | Х   | Х  | Х           | DSL                                      | Nop $\rightarrow$ Idle after t <sub>RFC</sub>               |       |

|                       | L  | Н   | Н   | н  | Х           | NOP                                      | Nop $\rightarrow$ Idle after tRFC                           |       |

|                       | L  | Н   | Н   | L  | Х           | BST                                      | Nop $\rightarrow$ Idle after t <sub>RFC</sub>               |       |

| Refreshing            | L  | Н   | L   | Х  | Х           | READ/WRIT                                | ILLEGAL                                                     |       |

|                       | L  | L   | Н   | Х  | Х           | ACT/PRE/PREA                             | ILLEGAL                                                     |       |

|                       | L  | L   | L   | х  | х           | AREF/SELF/<br>MRS/EMRS                   | ILLEGAL                                                     |       |

|                       | Н  | Х   | Х   | Х  | Х           | DSL                                      | Nop $\rightarrow$ Idle after t <sub>MRD</sub>               |       |

|                       | L  | н   | Н   | Н  | Х           | NOP                                      | Nop $\rightarrow$ Idle after t <sub>MRD</sub>               |       |

| Mode                  | L  | Н   | Н   | L  | Х           | BST                                      | ILLEGAL                                                     |       |

| register<br>accessing | L  | н   | L   | Х  | Х           | READ/WRIT                                | ILLEGAL                                                     |       |

| 3                     | L  | L   | х   | Х  | х           | ACT/PRE/PREA/<br>AREF/SELF/<br>MRS/ EMRS | ILLEGAL                                                     |       |

----

.

Notes:

1. All entries assume that CKE was active (High level) during the preceding clock cycle and the current clock cycle. (CKEn-1 = CKEn = "1")

3. Illegal to bank in specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

- 4. Illegal if tRCD is not satisfied.

- 5. Illegal if tRAS is not satisfied.

- 6. Must satisfy burst interrupt condition.

- 7. Must avoid bus contention, bus turn around, and/or satisfy write recovery requirements.

- 8. Must mask preceding data which don't satisfy twr.

Remark: H = High level, L = Low level, X = High or Low level (Don't care), V = Valid data

<sup>2.</sup> Illegal if any bank is not idle.

| Current                                 | CI  | ΚE |    |     |     |    | Address |                                                          | Netco |

|-----------------------------------------|-----|----|----|-----|-----|----|---------|----------------------------------------------------------|-------|

| State                                   | n-1 | n  | CS | RAS | CAS | WE | Address | Action                                                   | Notes |

|                                         | Н   | Х  | Х  | Х   | Х   | Х  | Х       | N/A                                                      |       |

|                                         | L   | Н  | Н  | Х   | Х   | Х  | Х       | Exit Self Refresh $\rightarrow$ Idle after tRFC          |       |

| 0 1 1                                   | L   | Н  | L  | Н   | Н   | Н  | Х       | Exit Self Refresh $\rightarrow$ Idle after tRFC          |       |

| Self refresh                            | L   | Н  | L  | Н   | L   | Х  | Х       | ILLEGAL                                                  |       |

|                                         | L   | Н  |    |     |     |    |         |                                                          |       |

|                                         | L   | L  | Х  | Х   | Х   | Х  | Х       | Maintain Self Refresh                                    |       |

|                                         | Н   | Х  | Х  | Х   | Х   | Х  | Х       | N/A                                                      |       |

|                                         |     |    | Н  | Х   | Х   | Х  | Х       |                                                          |       |

| Power-Down                              | L   | Н  | L  | Н   | Н   | Н  | Х       | - Exit Power Down $\rightarrow$ Idle after 1 clock cycle |       |

| LL                                      |     | L  | Х  | Х   | Х   | Х  | Х       | Maintain Power-Down                                      |       |

|                                         | Н   | Х  | Х  | Х   | Х   | Х  | Х       | N/A                                                      |       |

| Deep Power-<br>Down                     | L   | Н  | Х  | Х   | Х   | Х  | Х       | Exit Deep Power-Down $\rightarrow$ Exit Sequence         |       |

| L L                                     |     | L  | Х  | Х   | Х   | Х  | Х       | Maintain Deep Power-Down                                 |       |

|                                         | Н   | Н  | Х  | Х   | Х   | Х  | Х       | Refer to Function Truth Table                            |       |

|                                         | Н   | L  | Н  | Х   | Х   | Х  | Х       | Enter Power-down                                         | 2     |

|                                         | Н   | L  | L  | Н   | Н   | Н  | Х       | Enter Power-Down                                         | 2     |

|                                         | Н   | L  | L  | Н   | Н   | L  | Х       | Enter Deep Power-Down                                    | 3     |

| All banks idle                          | Н   | L  | L  | L   | L   | Н  | Х       | Self Refresh                                             | 1     |

|                                         | Н   | L  | L  | Н   | L   | Х  | Х       | ILLEGAL                                                  |       |

|                                         | Н   | L  | L  | L   | Х   | Х  | Х       | ILLEGAL                                                  |       |

|                                         | L   | Х  | Х  | Х   | Х   | Х  | Х       | Power-Down                                               | 2     |

|                                         | Н   | Н  | Х  | Х   | Х   | Х  | Х       | Refer to Function Truth Table                            |       |

|                                         | Н   | L  | Н  | Х   | Х   | Х  | Х       | Enter Power down                                         | 2     |

|                                         | Н   | L  | L  | Н   | Н   | Н  | Х       | Enter Power down                                         | 2     |

| Row Active                              | Н   | L  | L  | L   | L   | Н  | Х       | ILLEGAL                                                  |       |

|                                         | Н   | L  | L  | н   | L   | Х  | Х       | ILLEGAL                                                  |       |

|                                         | Н   | L  | L  | L   | Х   | Х  | Х       | ILLEGAL                                                  |       |

|                                         | L   | Х  | Х  | Х   | Х   | Х  | Х       | Power-Down $\rightarrow$ Row Active or Maintain PD       |       |

| Any state<br>other than<br>listed above | Н   | Н  | х  | x   | х   | х  | х       | Refer to Function Truth Table                            |       |

# 7.1.3 Functional Truth Table for CKE

Notes:

1. Self refresh can enter only from the all banks idle state.

2. Power-down can enter only from the all banks idle or row active state.

Deep power-down can enter only from the all banks idle state.

Remark: H = High level, L = Low level, X = High or Low level (Don't care), V = Valid data

$(\overline{RAS} = L, \overline{CAS} = H, \overline{WE} = H, BA0, BA1 = Bank, A0~An = Row Address)$

The Bank Activate command activates the bank designated by the BA (Bank Select) signal.

Row addresses are latched on A0~An when this command is issued and the cell data is read out to the sense amplifiers. The maximum time that each bank can be held in the active state is specified as tRAS (max).

# 7.1.5 Bank Precharge Command

$(\overline{RAS} = L, \overline{CAS} = H, \overline{WE} = L, BA0, BA1 = Bank, A10 = L)$

The Bank Precharge command is used to close (or precharge) the bank that is activated. Using this command, systems can designated the bank to be closed by specifying the BA address bit setting in the command set. A Precharge command can be used to precharge each bank separately (Bank Precharge) or all four banks simultaneously (Precharge All). After the Bank Precharge command is issued, any one bank can close, and the closed bank transitions from the active state to the idle state. To re-activate the closed bank, a system has to wait the minimum tRP delay after issuing the Precharge command before issuing the Active Command for the device to complete the Precharge operation.

### 7.1.6 Precharge All Command

$(\overline{RAS} = L, \overline{CAS} = H, \overline{WE} = L, BA0, BA1 = Don't care, A10 = H)$

The Precharge All command is used to precharge all banks simultaneously. After this command is issued, all four banks close and transition from the active state to the idle state.

#### 7.1.7 Write Command

$(\overline{RAS} = H, \overline{CAS} = L, \overline{WE} = L, BA0, BA1 = Bank, A10 = L)$

The Write command initiates a Write operation to the bank selected by BA0 and BA1 address inputs. The write data is latched at the positive edge of CLK. Users should preprogram the length of the write data (Burst Length) and the column access sequence (Addressing Mode) by setting the Mode Resister at power-up prior to using the Write command.

#### 7.1.8 Write with Auto Precharge Command

$(\overline{RAS} = H, \overline{CAS} = L, \overline{WE} = L, BA0, BA1 = Bank, A10 = H)$

The Write with Auto Precharge command performs the Precharge operation automatically after the Write operation. The internal precharge starts in the cycles immediately following the cycle in which the last data is written independent of CAS Latency.

#### 7.1.9 Read Command

$(\overline{RAS} = H, \overline{CAS} = L, \overline{WE} = H, BA0, BA1 = Bank, A10 = L)$

The Read command performs a Read operation to the bank designated by BA0-1. The read data is issued sequentially synchronized to the positive edges of CLK. The length of read data (Burst Length), Addressing Mode and CAS Latency (access time from  $\overline{CAS}$  command in a clock cycle) must be programmed in the Mode Register at power-up prior to the Write operation.

### 7.1.10 Read with Auto Precharge Command

$(\overline{RAS} = H, \overline{CAS} = L, \overline{WE} = H, BA0, BA1 = Bank, A10 = H)$

The Read with Auto Precharge command automatically performs the Precharge operation after the Read operation. When the CAS Latency = 3, the internal precharge starts two cycles before the last data is output. When the CAS Latency = 2, the internal precharge starts one cycle before the last data is output.

7.1.11 Extended Mode Register Set Command

$(\overline{RAS} = L, \overline{CAS} = L, \overline{WE} = L, BA1, A0 \sim An = Register Data)$

The Extended Mode Register Set command is designed to support Partial Array Self Refresh, Temperature Compensated Self Refresh, and Output Driver Strength/Size by allowing users to program each value by setting predefined address bits. The default values in the Extended Mode Register after power-up are undefined; therefore this command must be issued during the power-up sequence. Also, this command can be issued while all banks are in the idle state.

**The set winbond**

#### 7.1.12 Mode Register Set Command

$(\overline{RAS} = L, \overline{CAS} = L, \overline{WE} = L, BA1, A0~An = Register Data)$

The Mode Register Set command is used to program the values of CAS latency, Addressing Mode and Burst Length in the Mode Register. The default values in the Mode Register after power-up are undefined; therefore this command must be issued during the power-up sequence and re-issued after the Deep Power Down Exit Command. Also, this command can be issued while all banks are in the idle state.

### 7.1.13 No-Operation Command

$(\overline{RAS} = H, \overline{CAS} = H, \overline{WE} = H)$

The No-Operation command is used in cases such as preventing the device from registering unintended commands. The device performs no operation when this command is registered. This command is functionally equivalent to the Device Deselect command.

#### 7.1.14 Burst Stop Command

$(\overline{RAS} = H, \overline{CAS} = H, \overline{WE} = L)$

The Burst stop command is used to stop the already activated burst operation. The activated page is left unclosed and future commands can be issued to access the same page of the active bank. If this command is issued during a burst read operation, the read data will go to a Hi-Z state after a delay equal to the CAS latency. If a burst stop command is issued during a burst write operation, then the burst data is terminated and data bus goes to Hi-Z at the same clock that the burst command is activated. Any remaining data from the burst write cycle is ignored.

#### 7.1.15 Device Deselect Command

$(\overline{CS} = H)$

The Device Deselect command disables the command decoder so that the  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and Address inputs are ignored. This command is similar to the No-Operation command.

#### 7.1.16 Auto Refresh Command

$(\overline{RAS} = L, \overline{CAS} = L, \overline{WE} = H, CKE = H, BA0, BA1, A0~An = Don't care)$

The Auto Refresh command is used to refresh the row address provided by the internal refresh counter. The Refresh operation must be performed 8192 times within 64 mS. The next command can be issued after tRC from the end of the Auto Refresh command. When the Auto Refresh command is issued, All banks must be in the idle

state. The Auto Refresh operation is equivalent to the  $\overline{CAS}$  -before-  $\overline{RAS}$  operation in a conventional DRAM.

#### 7.1.17 Self Refresh Entry Command

$(\overline{RAS} = L, \overline{CAS} = L, \overline{WE} = H, CKE = L, BA0, BA1, A0~An = Don't care)$

When the Self Refresh Entry command is issued, the device enters the Self Refresh mode. While the device is in Self Refresh mode, the device automatically refreshes memory cells, and all input and I/O buffers (except the CKE buffer) are disabled. By asserting the CKE signal "high" (and by issuing the Self Refresh Exit command), the device exits the Self Refresh mode.

## 7.1.18 Self Refresh Exit Command

$(CKE = H, \overline{CS} = H \text{ or } CKE = H, \overline{RAS} = H, \overline{CAS} = H)$

This command is issued to exit out of the Self Refresh mode. One tRC delay is required prior to issuing any subsequent command from the end of the Self Refresh Exit command.

#### 7.1.19 Clock Suspend Mode Entry/Power Down Mode Entry Command

#### (CKE = L)

The internal CLK is suspended for one cycle when this command is issued (when CKE is asserted "low"). The device state is held intact while the CLK is suspended. On the other hand, when the device is not operating the Burst cycle, this command performs entry into Power Down mode. All input and output buffers (except the CKE buffer) are turned off in Power Down mode.

#### 7.1.20 Clock Suspend Mode Exit/Power Down Mode Exit Command

#### (CKE = H)

When the internal CLK has been suspended, operation of the internal CLK is resumed by providing this command (asserting CKE "high"). When the device is in Power Down mode, the device exits this mode and all disabled buffers are turned on to the active state. Any subsequent commands can be issued after one clock cycle from the end of this command.

#### 7.1.21 Data Write/Output Enable, Data Mask/Output Disable Command

#### (DQM = L/H or LDQM, UDQM = L/H or DQM0-3=L/H)

During a Write cycle, the DQM or LDQM, UDQM or DQM0-3 signals mask write data. Each of these signals control the input buffers per byte. During a Read cycle, the DQM or LDQM, UDQM or DQM0-3 signals control of the output buffers per byte.

| I/O Org. | Mask Pin | Masked DQs |

|----------|----------|------------|

| ×16      | LDQM     | DQ0~DQ7    |

| ×TO      | UDQM     | DQ8~DQ15   |

|          | DQM0     | DQ0~DQ7    |

| ×32      | DQM1     | DQ8~DQ15   |

| *32      | DQM2     | DQ16~DQ23  |

|          | DQM3     | DQ24~DQ31  |

# 8. OPERATION

### 8.1 Read Operation

Issuing the Bank Activate command to the idle bank puts it into the active state. When the Read command is issued after  $t_{RCD}$  from the Bank Activate command, the data is read out sequentially, synchronized to the positive edges of CLK (a Burst Read operation). The initial read data becomes available after CAS Latency from the issuing of the Read command. The CAS latency must be set in the Mode Register at power-up. In addition, the burst length of read data and Addressing Mode must be set. Each bank is held in the active state unless the Precharge command is issued, so that the sense amplifiers can be used as secondary cache.

When the Read with Auto Precharge command is issued, the Precharge operation is performed automatically after the Read cycle, then the bank is switched to the idle state. This command cannot be interrupted by any other commands. Also, when the Burst Length is 1 and tRCD (min), the timing from the  $\overrightarrow{RAS}$  command to the start of the Auto Precharge operation is shorter than t<sub>RAS</sub> (min). In this case, tRAS (min) must be satisfied by extending tRCD.

When the Precharge operation is performed on a bank during a Burst Read operation, the Burst operation is terminated.

When the Burst Length is full-page, column data is repeatedly read out until the Burst Stop command or Precharge command is issued.

# **FEESE Winbond**

# 8.2 Write Operation

Issuing the Write command after t<sub>RCD</sub> from the Bank Activate command, the input data is latched sequentially, synchronizing with the positive edges of CLK after the Write command (Burst Write operation). The burst length of the Write data (Burst Length) and Addressing Mode must be set in the Mode Register at power-up.

When the Write with Auto Precharge command is issued, the Precharge operation is performed automatically after the Write cycle, then the bank is switched to the idle state. This command cannot be interrupted by any other command for the entire burst data duration. Also, when the Burst Length is 1 and tRCD (min), the timing from the

RAS command to the start of the Auto Precharge operation is shorter than tRAS (min). In this case, tRAS (min) must be satisfied by extending tRCD.

When the Precharge operation is performed in a bank during a Burst Write operation, the Burst operation is terminated.

When the Burst Length is full-page, the input data is repeatedly latched until the Burst Stop command or the Precharge command is issued.

When the Burst Read and Single Write mode is selected, the write burst length is 1 regardless of the read burst length.

## 8.3 Precharge

There are two commands which perform the Precharge operation: Bank Precharge and Precharge All. When the Bank Precharge command is issued to the active bank, the bank is precharged and then switched to the idle state. The Bank Precharge command can precharge one bank independently of the other bank and hold the unprecharged bank in the active state. The maximum time each bank can be held in the active state is specified as tRAS (max). Therefore, each bank must be precharged within tRAS (max) from the Bank Activate command.

The Precharge All command can be used to precharge all banks simultaneously. Even if banks are not in the active state, the Precharge All command can still be issued. In this case, the Precharge operation is performed only for the active bank and the precharged bank is then switched to the idle state.

### 8.3.1 Auto Precharge

Auto precharge is a feature that performs the same individual-bank PRECHARGE function described previously, without requiring an explicit command. This is accomplished by using A10 to enable auto precharge in conjunction with a specific READ or WRITE command. A precharge of the bank/row that is addressed with the READ or WRITE command is automatically performed upon completion of the READ or WRITE burst, except in the continuous page burst mode where auto precharge does not apply. In the specific case of write burst mode set to single location access with burst length set to continuous, the burst length setting is the overriding setting and auto precharge does not apply. Auto precharge is nonpersistent in that it is either enabled or disabled for each individual READ or WRITE command.

Auto precharge ensures that the precharge is initiated at the earliest valid stage within a burst. Another command cannot be issued to the same bank until the precharge time (tRP) is completed. This is determined as if an explicit PRECHARGE command was issued at the earliest possible time.

Winbond SDRAM supports concurrent auto precharge; cases of concurrent auto precharge for READs and WRITEs are defined below.

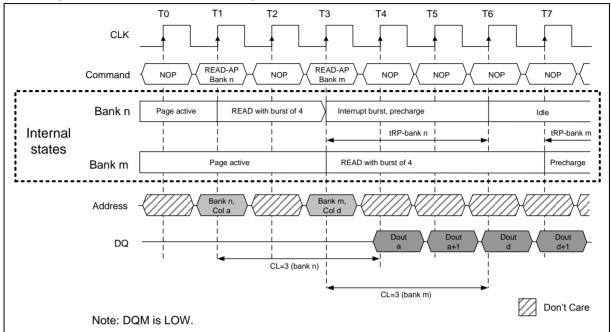

# 8.3.2 READ with auto precharge interrupted by a READ (with or without auto precharge)

winhnn

A READ to bank m will interrupt a READ on bank n following the programmed CAS latency. The precharge to bank n begins when the READ to bank m is registered.

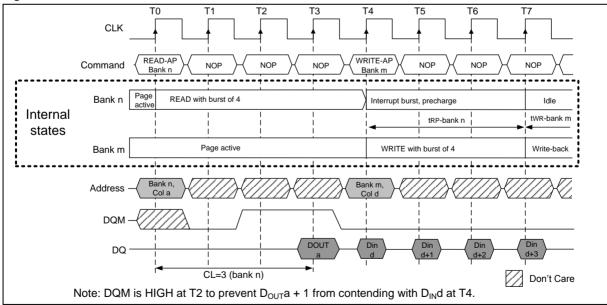

### 8.3.3 READ with auto precharge interrupted by a WRITE (with or without auto precharge)

A WRITE to bank m will interrupt a READ on bank n when registered. DQM should be used two clocks prior to the WRITE command to prevent bus contention. The precharge to bank n begins when the WRITE to bank m is registered.

# **\_\_\_\_** winbond \_\_\_\_

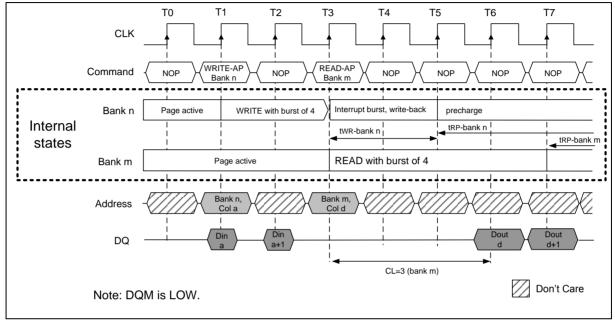

## 8.3.4 WRITE with auto precharge interrupted by a READ (with or without auto precharge)

A READ to bank m will interrupt a WRITE on bank n when registered, with the data-out appearing CL later. The precharge to bank n will begin after tWR is met, where tWR begins when the READ to bank m is registered. The last valid WRITE to bank n will be data in registered one clock prior to the READ to bank m.

### 8.3.5 WRITE with auto precharge interrupted by a WRITE (with or without auto precharge)

A READ to bank m will interrupt a WRITE on bank n when registered, with the data-out appearing CL later. The precharge to bank n will begin after tWR is met, where tWR begins when the READ to bank m is registered. The last valid WRITE to bank n will be data in registered one clock prior to the READ to bank m.

# **E**

## 8.4 Burst Termination

The Read or Write command can be issued on any clock cycle. Whenever a Read operation is to be interrupted by a Write command, the output data must be masked by DQM to avoid I/O conflict. Also, when a Write operation is to be interrupted by a Read command, only the input data before the Read command is enable and the input data after the Read command is disabled.

#### - Read Interrupted by a Precharge

A Precharge command can be issued to terminate a Burst cycle early. When a Burst Read cycle is interrupted by a Precharge command, the read operation is terminated after (CAS latency-1) clock cycles from the Precharge command.

#### - Write Interrupted by a Precharge

A burst Write cycle can be interrupted by a Precharge command, the input circuit is reset at the same clock cycle at which the Precharge command is issued. In this case, the DQM signal must be asserted high to prevent writing the invalid data to the cell array.

- Read Interrupted by a Burst Stop

When the Burst Stop command is issued for the bank in a Burst cycle, the Burst operation is terminated. When the Burst Stop command is issued during a Burst Read cycle, the read operation is terminated after clock cycle of (CAS latency-1) from the Burst Stop command.

#### - Write Interrupted by a Burst Stop

When the Burst Stop command is issued during a Burst Write cycle, the write operation is terminated at the same clock cycle that the Burst Stop command is issued.

- Write Interrupted by a Read

A burst of write operation can be interrupted by a read command. The read command interrupts the write operation on the same clock that the read command is issued. All the burst writes that are presented on the data bus before the read command is issued will be written to the memory. Any remaining burst writes will be ignored once the read command is activated. There must be at least one clock bubble (Hi-Z state) on the data bus to avoid bus contention.

#### - Read Interrupted by a Write

A burst of read operation can be interrupted by a write command by driving output drivers in a Hi-Z state using DQM before write to avoid data conflict. DQM should be utilized if there is data from a Read command on the first and second cycles of the subsequent write cycles to ensure the read data are tri-stated. From the third clock cycle, the write command will control the data bus and DQM is not needed.

# **E**

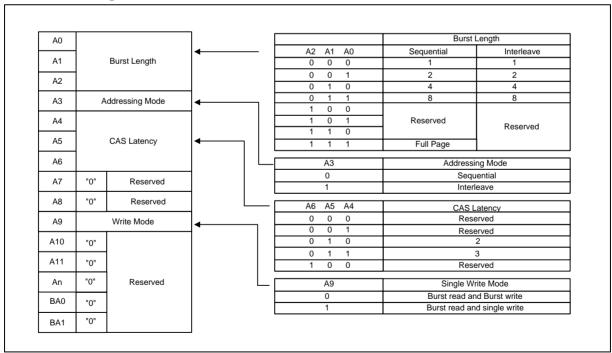

# 8.5 Mode Register Operation

The Mode register designates the operation mode for the Read or Write cycle. This register is divided into three fields; A Burst Length field to set the length of burst data, an Addressing Mode selected bits to designate the column access sequence in a Burst cycle, and a CAS Latency field to set the access time in clock cycle.

The Mode Register is programmed by the Mode Register Set command when all banks are in the idle state. The data to be set in the Mode Register is transferred using the A0~An, BA0, BA1 address inputs. The initial value of the Mode Register after power-up is undefined; therefore the Mode Register Set command must be issued before proper operation.

# 8.5.1 Burst Length field (A2~A0)

This field specifies the data length for column access using the A2 $\sim$ A0 pins and sets the Burst Length to be 1, 2, 4, 8, words, or full-page.

| A2 | A1 | A0 | Bust Length |

|----|----|----|-------------|

| 0  | 0  | 0  | 1 word      |

| 0  | 0  | 1  | 2 words     |

| 0  | 1  | 0  | 4 words     |

| 0  | 1  | 1  | 8 words     |

| 1  | 1  | 1  | Full-Page   |

## 8.5.2 Addressing Mode Select (A3)

The Addressing Mode can be one of two modes; Interleave mode or Sequential mode. When the A3 bit is 0, Sequential mode is selected. When the A3 bit is 1, Interleave mode is selected. Both Addressing modes support burst length of 1, 2, 4 and 8 words. Additionally, Sequential mode supports the full-page burst.

| A3 | Addressing Mode |

|----|-----------------|

| 0  | Sequential      |

| 1  | Interleave      |

### 8.5.3 Addressing Sequence for Sequential Mode

A column access is performed by incrementing the column address input to the device. The address is varied by the Burst Length shown as below table.

| DATA   | Access Address | Burst Length                        |

|--------|----------------|-------------------------------------|

| Data 0 | n              | 2 words (Address bit is A0)         |

| Data 1 | n + 1          | not carried from A0 to A1           |

| Data 2 | n + 2          | 4 words (Address bit is A1, A0)     |

| Data 3 | n + 3          | not carried from A1 to A2           |

| Data 4 | n + 4          |                                     |

| Data 5 | n + 5          | 8 words (Address bit is A2, A1, A0) |

| Data 6 | n + 6          | not carried from A2 to A3           |

| Data 7 | n + 7          | V                                   |

# **FEESE Winbond**

# 8.5.4 Addressing Sequence for Interleave Mode

A column access is started from the input column address and is performed by inverting the address bits in the sequence shown as below table.

| DATA   | Access Address             | Burst Length |

|--------|----------------------------|--------------|

| Data 0 | A8 A7 A6 A5 A4 A3 A2 A1 A0 | 2 words      |

| Data 1 | A8 A7 A6 A5 A4 A3 A2 A1 A0 |              |

| Data 2 | A8 A7 A6 A5 A4 A3 A2 A1 A0 | 4 words      |

| Data 3 | A8 A7 A6 A5 A4 A3 A2 A1 A0 | J            |

| Data 4 | A8 A7 A6 A5 A4 A3 A2 A1 A0 | 8 words      |

| Data 5 | A8 A7 A6 A5 A4 A3 A2 A1 A0 |              |

| Data 6 | A8 A7 A6 A5 A4 A3 A2 A1 A0 |              |

| Data 7 | A8 A7 A6 A5 A4 A3 A2 A1 A0 | V            |

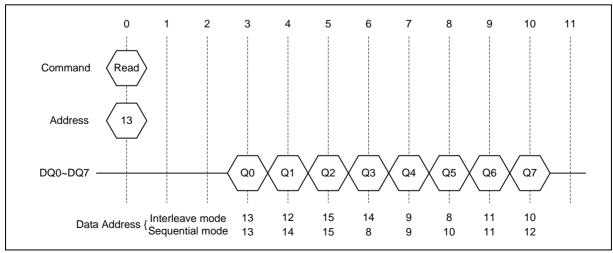

## 8.5.5 Addressing Sequence Example (Burst Length = 8 and Input Address is 13)

| Dete  |    | Interleave Mode |    |    |    |    |    | de |    | Sequer | tial Mode |     |                                   |

|-------|----|-----------------|----|----|----|----|----|----|----|--------|-----------|-----|-----------------------------------|

| Data  | A8 | A7              | A6 | A5 | A4 | A3 | A2 | A1 | A0 | ADD    |           | ADD |                                   |

| Data0 | 0  | 0               | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 13     | 13        | 13  |                                   |

| Data1 | 0  | 0               | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 12     | 13 + 1    | 14  |                                   |

| Data2 | 0  | 0               | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 15     | 13 + 2    | 15  | calculated using                  |

| Data3 | 0  | 0               | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 14     | 13 + 3    | 8   | A2, A1 and A0 bits not carry from |

| Data4 | 0  | 0               | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 9      | 13 + 4    | 9   | A2 to A3 bit.                     |

| Data5 | 0  | 0               | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 8      | 13 + 5    | 10  |                                   |

| Data6 | 0  | 0               | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 11     | 13 + 6    | 11  |                                   |

| Data7 | 0  | 0               | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 10     | 13 + 7    | 12  |                                   |

### 8.5.6 Read Cycle CAS Latency = 3

Publication Release Date: Dec. 01, 2016 Revision: A01-002

# **THEFT Winbond**

# 8.5.7 CAS Latency field (A6~A4)

This field specifies the number of clock cycles from the assertion of the Read command to the first data read. The minimum values of CAS Latency depends on the frequency of CLK. The minimum value which satisfies the following formula must be set in this field.

| A6 | A5 | A4 | CAS Latency |

|----|----|----|-------------|

| 0  | 1  | 0  | 2 clock     |

| 0  | 1  | 1  | 3 clock     |

#### • Reserved bits (A7, A8, A10, A11, An, BA0, BA1)

These bits are reserved for future operations. They must be set to 0 for normal operation.

#### • Single Write mode (A9)

This bit is used to select the write mode. When the A9 bit is 0, Burst Read and Burst Write mode are selected. When the A9 bit is 1, Burst Read and Single Write mode are selected.

| A9 | Write Mode                  |

|----|-----------------------------|

| 0  | Burst Read and Burst Write  |

| 1  | Burst Read and Single Write |

### 8.5.8 Mode Register Definition

# **The second second**

# 8.6 Extended Mode Register Description

The Extended Mode Register designates the operation condition while SDRAM is in Self Refresh Mode and selects the output driver strength as full, 1/2, 1/4, or 1/8 strength. The register is divided into two fields; (1) Partial Array Self Refresh field selects how much banks or which part of a bank need to be refreshed during Self Refresh. (2) Driver Strength selected bit to control the size of output buffer. The initial value of the Extended Mode Register after power-up is Full Driver Strength, and all banks are refreshed during Self Refresh Mode.

|     |                                                         |                                                                                                                                                                                                                                                                                                                                   | A2 A1 A0                                                            | Self-Refresh coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pa  | rtial Array                                             |                                                                                                                                                                                                                                                                                                                                   | 0 0 0                                                               | All banks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |